Controlled Impedance on High-Speed Flex PCBs

Front-end analysis can help estimate the proper hatch opening – if any – for a flex PCB.

by Zachariah Peterson

Flex PCB and rigid-flex PCB designers are aware of the typical lack of ground planes in a flex design. Due to this and the obvious requirement of ground planes in high-speed PCBs and RF PCBs, one may think that flex PCBs cannot support high-speed digital signals. However, even with a mesh or hatched ground plane, it is possible to design systems that include high-speed signals, both single-ended and differential.

Of course, there are limitations on using hatched ground planes to support high-speed digital signals. For differential interfaces, the hatch has the potential to induce skew, but the superposition of the electromagnetic field from differential signals helps ensure lower noise. In contrast, single-ended signals without a nearby solid reference have the potential for greater radiated emissions from a flex PCB with a hatched ground plane.

Here we discuss some of the limiting factors for both single-ended and differential signals used in flex PCBs and offer some simulation data that illustrates bandwidth limits. Some simple estimators can also be used to determine when a hatched plane is no longer capable of supporting digital signals due to its periodic deviation in input impedance.

Hatched Planes and Input Impedance

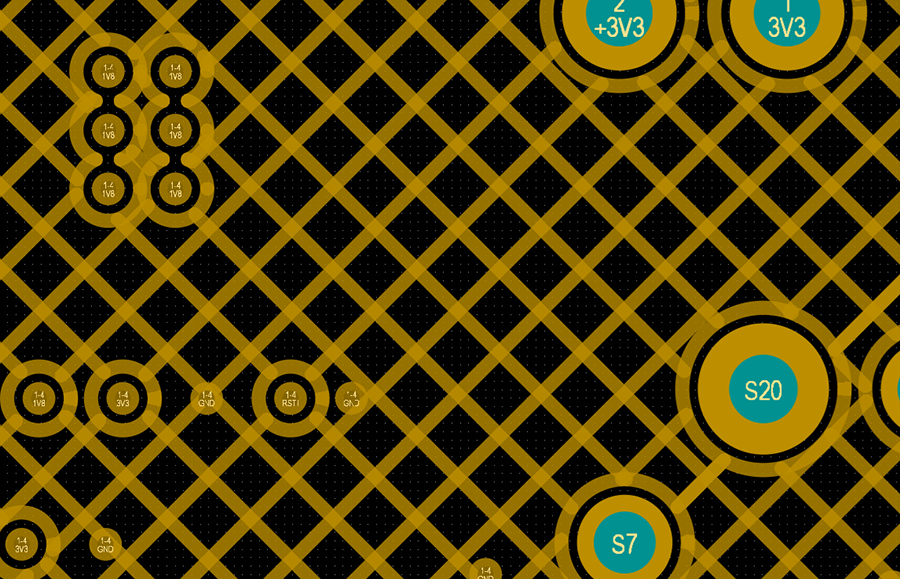

In a flex PCB or on the flexible section of a rigid-flex PCB, a hatched ground plane can be used on one layer to provide some level of support for return paths. A hatched ground plane has a lattice structure, as shown in Figure 1. The lattice structure permits the flexible region to repeatedly bend if required. It can be used on its own layer or in a coplanar configuration if needed.

Because the hatched plane contains copper gaps in the latticework, a trace routed over a hatched plane will exhibit periodic variations in its input impedance. Although we typically do not do this, the magnitude and periodicity of the variations for a straight run of a single-ended or differential transmission line can be predicted from empirical models based on measurement data.

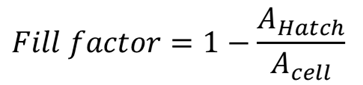

One way to quantify or index the expected variation in trace impedance over a hatched ground plane is to describe the plane using a fill factor. The fill factor of the structure can be defined as the ratio of the area occupied by copper to the area of a repeating cell or element in the hatched plane. Mathematically, we can express this in Figure 2.

While an analytical model that uses the fill factor to predict impedance does not exist, one could develop an empirical model based on S-parameter measurements on various flex PCB stackups. In addition, one should not expect the relationship to be linear due to the general nonlinearity of stripline and microstrip impedance. This applies to both single-ended and differential transmission lines.

Another factor to consider is variance in input impedance, which will be a function of frequency. Variation in the input impedance will depend on the fill factor, although this would vary to different degrees for single-ended and differential signals. The variation arises because the input impedance depends on the length of copper discontinuity due to gaps in the hatched ground plane.

At low frequencies, the hatched plane will resemble a solid ground plane because the impedance discontinuities appear to be very small when a signal wavelength is much larger than the impedance discontinuity. At higher frequencies, we would expect significant deviations in S-parameter plots when we compare a trace over a solid ground plane versus the same trace and termination over a hatched ground plane.

Single-Ended Transmission Lines

With single-ended traces, the trace impedance is determined by the distance to ground and the width of the trace. The copper weight also plays a role but is less important when the traces are much wider than the copper foil’s thickness. The channel bandwidth required for high-speed single-ended interfaces is quite small, topping out below 1GHz for common serial interfaces. For an interface like DDR, which uses groups of single-ended traces, channel bandwidth per trace is still quite low in the GHz range.

This means that, although single-ended traces in serial interfaces like SPI do exhibit variation in the characteristic impedance, they tend to be more tolerant of the ground plane hatching due to the low channel bandwidth requirement. Gaps in the hatching pattern must be very large to be noticeable by a signal on an SPI bus, for example. If we take a typical load capacitance of an SPI bus of 30pF, we can use the channel bandwidth limit to approximate the maximum gap size of the hatching pattern, assuming our impedance deviation demands a 20% limit on the size of the discontinuity. A very simple critical length calculation gives a rough estimate (Figure 3).

As long as the gap size is well below this maximum value, we likely do not need to worry about the signal integrity of the SPI bus, but this should be verified through testing on an oscilloscope. Note that this makes some broad assumptions, particularly the relation given the allowed impedance deviation the bus can tolerate, the limit this imposes in critical length, and the fact that the traces are already so short that the 30pF load capacitance is limiting the rise time. On long flex cables, this third point may not hold at all. However, this gives us a very generous gap size allowance, much larger than what is typically seen in hatched ground planes.

This does not address the potential for radiated emissions when the bus is quite large or when many single-ended signals are switching on the same bus. The ground plane hatching has some shielding effectiveness, which depends on the fill factor. A low fill factor might be fine for a single SPI signal, but it may admit too much radiated emission when a large number of SPI signals or GPIOs are routed over the hatched ground plane. This factor can only be accounted for in simulation or testing, or with empirical models from the research literature.

Differential Pairs

Differential pairs have an additional parameter that can be used to tune the interconnect’s impedance. That parameter is the spacing between the traces in the differential pair. Each trace functions as a return path for the other trace, and the spacing between them can be exploited to overcome a lack of ground below the differential pair.

This is important because differential interfaces can operate at multi-gigahertz speeds, which places the channel bandwidths in the multi-gigahertz range. While we don’t expect extreme designs with 100G per lane routing on flex PCBs, some designs – such as sensor platforms or vision systems – definitely use interfaces with gigahertz channel bandwidth requirements. For example, JESD240 or MIPI standards might be routed on these PCBs, which would require accounting for high channel bandwidth requirements.

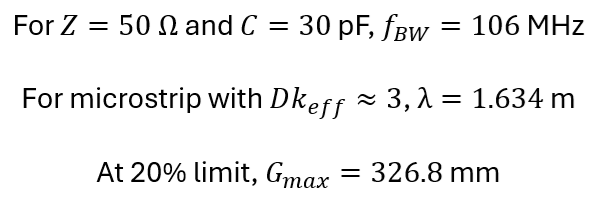

Figure 4 shows an example S-parameter plot. This insertion loss plot is for a differential pair over a hatched ground plane and illustrates when severe losses start to arise due to the copper discontinuities in the hatched ground plane.

For differential pairs, these losses might be reduced or shifted in two ways:

- By changing the spacing between the traces in the differential pair

- By changing the hatch opening

- By changing the thickness of the flex substrate material.

Decreasing the hatch opening size will push the frequency to higher values where insertion loss dips appear. I have not investigated the effect of changing spacing and thickness on the frequencies of insertion loss, but I would expect that changing these values will only change the magnitude of those losses rather than the frequency. Due to trace-to-trace coupling in a differential pair, one would expect that decreasing the spacing will decrease radiated emissions and reduce the severity of insertion loss.

Front-End Flex PCB Analysis and Simulation

Before start routing over a hatched ground plane in a flex PCB, a bit of front-end analysis can help estimate the appropriate hatch opening that will preserve signal integrity and still be manufacturable. If extremely small hatch openings are required for a very high-speed interface, a better option may be a cable that can carry the signal rather than attempting a flex design. Electromagnetic simulation software for PCBs can help validate this, or an experienced design firm can help determine the best approach.

Ed: This article was originally published on Northwest Engineering Solutions’ blog.

Zachariah Peterson has an extensive technical background in academia and industry. He runs Northwest Engineering Solutions (nwengineeringllc.com), a PCB design and technical marketing firm that serves industrial automation, defense and EDA software clients; zmp@nwengineeringllc.com. He is speaking at PCB East in April.