Splitting a PCB for Concurrent Design

As PCB designs grow more complex, partitioning and teamwork become part of the layout strategy.

Printed circuit board design grows in complexity with each passing year. Many protocols must be implemented. An ASIC (application-specific integrated circuit) or an FPGA (field-programmable gate array) may be the center of attention, but there will likely be a memory bus along with other architectures, such as ethernet or USB, to move data around. Interacting with the world around us requires some sort of sensor to read the room, while other circuits are used to feed this processed data back to the user.

As mixed-signal designs become more common, it makes sense to divvy up the work to those who have the necessary skills. Printed circuit board designers tend to fall into a specialty. Their first job becomes an anchor that pulls them back to that same technology.

At least, that’s how it worked for me and an analog layout. I didn’t see a DDR (double data rate) memory device until 2013. By 2017, the DDR was stacked above the processor, eliminating the routing effort altogether. When I saw my first Xbox One X main logic board, the DDR5 was a beautiful 12-package array, locked down and off-limits. While I have struggled through the constraint capture and routing of a smaller DDR3 memory circuit, I’ll never be an expert.

The process of compartmentalizing the board must follow high-level placement as a minimum. This floor planning revolves around the SI/PI goals. Identifying and capturing the design parameters is a must before anything gets turned loose. As the owner of the deliverables, it’s best to concentrate on the PDN study since it’s everywhere. You can optimize bottlenecks and other conflicts of interest early in the design cycle.

The second priority when defining a partition is to minimize the number of connections to and from the circuit block. The overall placement will drive data flow. Routing to an SD card or some other I/O is often suboptimal in terms of trace length. These inevitable rivers of traces can and will be routed from one partition to another. The person working inside the box will see where the traces come in and can go from there.

Our use case involves a service bureau and an internal resource, with me in the driver’s seat. A hierarchical schematic may not be for everyone, but in this case, it allowed us to decouple from the wireless portion of the design. That’s a high-touch effort, so we kept it in-house. For reference, this was a breakout board for a smartphone. The main function was to measure current, plus the typical P1 experiments you do when it’s two years before production starts.

The RF section was essentially “set it and forget it.” My day-to-day area of concern took place under the footprint of the Qualcomm chip. At that point in time, the chip didn’t exist, and neither did a reference design. I got to fan out my very own Snapdragon!

The power integrity engineer sent me back to the drawing board three times before signing off. It came with a warning not to change any of the shapes, not even a little. It was then that I understood why Qualcomm staff told me not to touch the SoC while routing the SDIO (secure digital input/output) lines back in the day. Mobile chips are very sensitive to power distribution. Solving all this drama makes me want to stick with radio boards.

Meanwhile, the service bureau had a large board area sectioned off with some big connectors on one end and a whole bunch of op amps and sense resistors to enable across the board. I fanned out one big connector to the LC filters and told them to do the others the same way. Leaving them a few examples was better than hoping that they could read my mind.

At some point, all these things had to be brought back together under one design. Importing the completed section could take a few hours. I learned some things about documenting what’s inside the partition before sharing. It’s very easy to list the components in an area.

It would have saved me some time to set up the display and other options with a script. Playing back the script would have reset the environment to its exact conditions so everything would come back as planned. I encourage satellite workers to start a script that can play back their contribution if the reimport process runs into a jam.

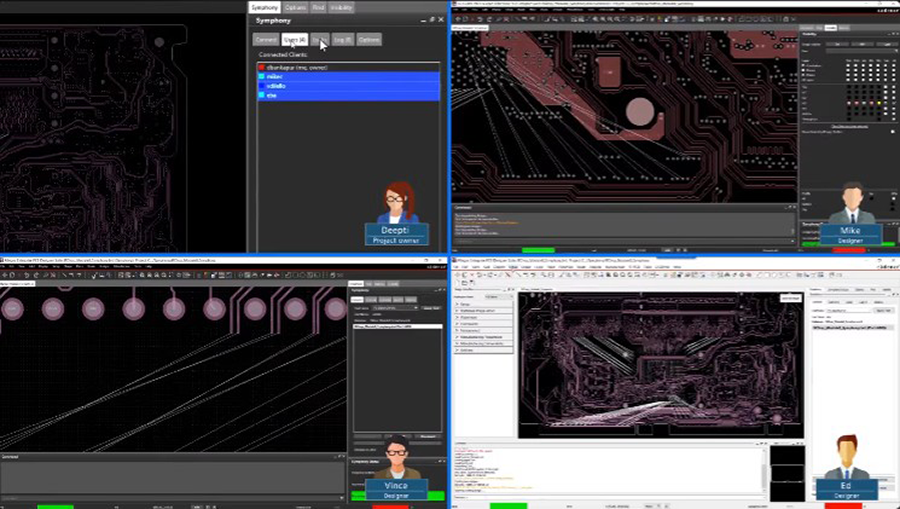

With the process limits of this approach in mind, the key players creating enormous printed circuit boards will take a fully networked approach to design. A team of designers can combine efforts in real time with a single networked database.

A certain mojo goes along with online role-playing games. People with similar personality defects form bonds while going through video game battles against space monsters or villains. That kind of “solve it to win” scenario can also be found when three people are distilling strategy into tactics that solve a printed circuit board with “a million” pins.

Having a few subject matter experts in your corner sounds like a good deal.End of article content

John Burkhert, Jr. is a principle PCB designer in retirement. For the past several years, he has been sharing what he has learned for the sake of helping fresh and ambitious PCB designers. The knowledge is passed along through stories and lessons learned from three decades of design, including the most basic one-layer board up to the high-reliability rigid-flex HDI designs for aerospace and military applications. His well-earned free time is spent on a bike, or with a mic doing a karaoke jam.