# PRINCEPORE DESIGNATION DESIGNA

# ARE OLD IDEAS ABOUT TO TAKE OFF? READY FOR READY FOR LIFTOFF

Thermal Interface Materials Warpage Measurement Are OEMs Changing their EMS Providers?

### **PROTOTYPES** FROM TAIWAN

### No Tariffs! Best Quality and Price!

#### Technology:

Up to 50 Layers Any Layer HDI Sequential Lamination Blind / Buried Vias Laser Drilling / Routing Heavy Copper

#### Materials:

Fr4 Metal Core Isola Rogers Polyimide - Flex Magtron

www.PCB4u.com sales@PCB4u.com Tel: (408) 748-9600 2986 Scott Blvd., Santa Clara, CA 95054 SAM & ITAR Registered UL E333047 ISO 9001 - 2015

RUSHPCB

20 YEARS OF MANUFACTURING EXPERIENCE WITH BLIND AND BURIED VIAS, RIGID FLEX & FLEX PCB ELECTRONIC DESIGN, & QUICK TURN CIRCUIT BOARDS, ASSEMBLY & FULL TURNKEY

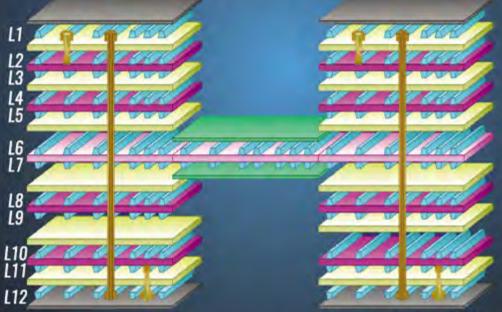

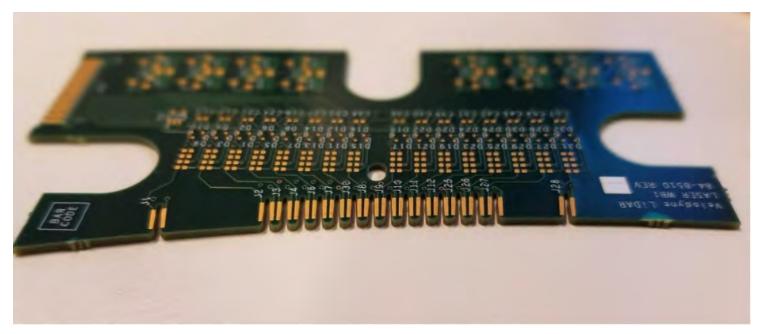

# Multilayer PCB Stackup

12 Layer Flex Rigid, 0.030" Thick Rigid, 0.008" Thick Flex Blind Via L1-L2 & L11-L12, 0.003" Hole, Resin Filled, 0.002"/0.002" Trace/Space, Controlled Impedance

Manufactured on August 2016

### When you're in a rush call RUSH PCB

Affordable Pricing \* Satisfaction Guarantee \* Fast Response \* Free Quote \* Fast Shipping HDI Boards \* Stacked Micro Vias \* 2 mil line & Space \* Flex & Rigid Flex

### Located in the Silicon Valley PCB up to 12 Layers in 3 days PCB Assembly Same Day Turn Full Turnkey Service

Certified: ISO9001/ITAR/UL www.rushpcb.com | Sales@rushpcb.com | 1 408 496 6013 Rush PCB Inc, 2149-20 O'Toole Ave, San Jose, CA 95131, U.S.A

#### AUGUST 2023 • VOL. 40 • NO. 8

### PRINTED CIRCUIT DESIGN & FAB CIRCUITS ASSEMBLY

#### FEATURES

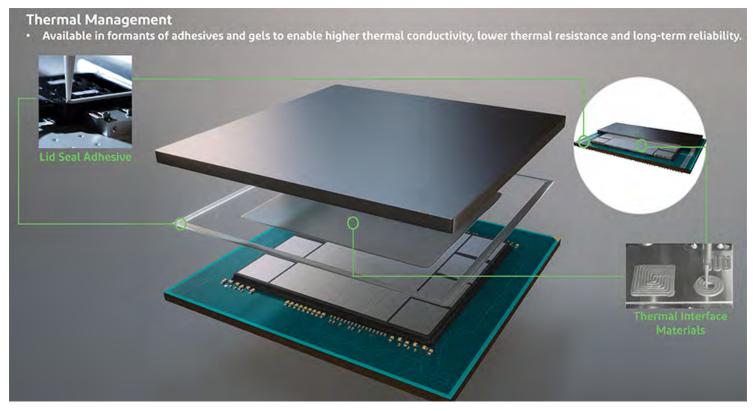

#### THERMAL MANAGEMENT

#### The Heat is On

Thermal interface materials (TIM) are used between components to help with heat dissipation. Claire Wemp, Ph.D., a thermal applications engineer at DuPont, discusses the use of TIMs, as well as her involvement in the Society of Women Engineers. by MIKE BUETOW

**PACKAGING** (COVER STORY)

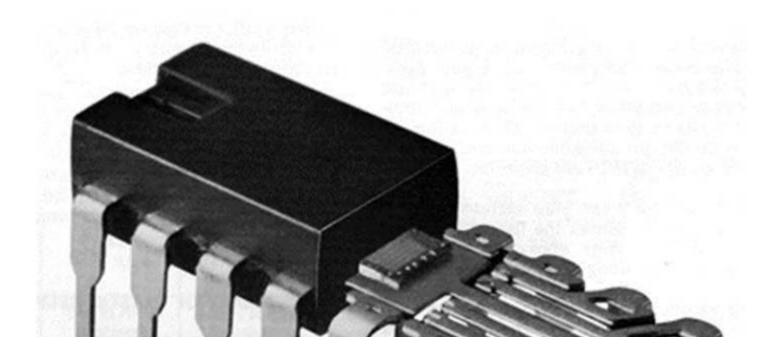

#### A Plethora of Pitches

The evolution of integrated circuit package technology

drove the electronics industry to its present state, but a closer look at the past reveals missed opportunities to create a more coherent set of IC standards, as well as lessons to be learned for future choices to improve design efficacy and product performance and reliability.

by JOSEPH FJELSTAD

#### **INSPECTION**

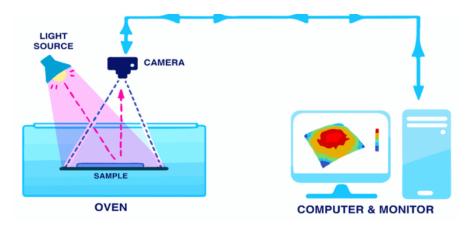

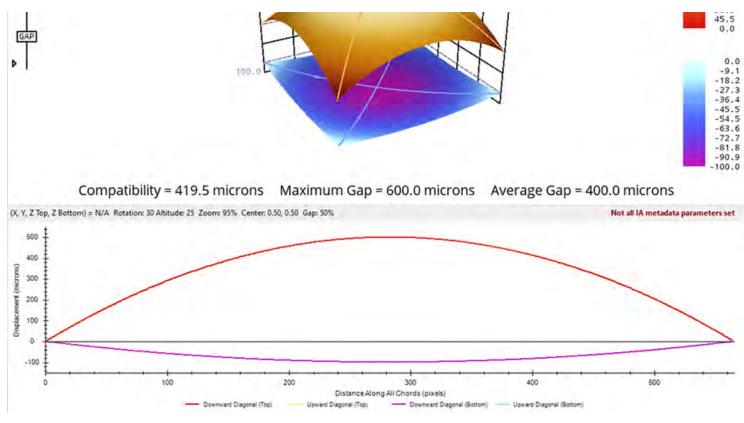

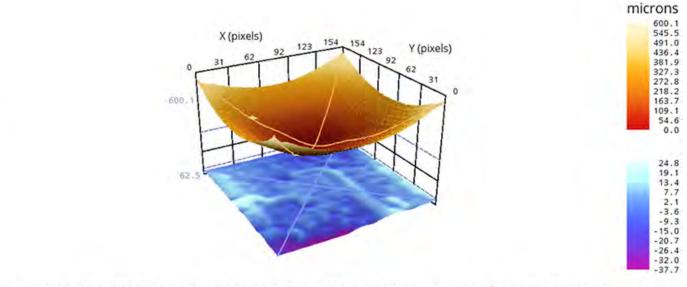

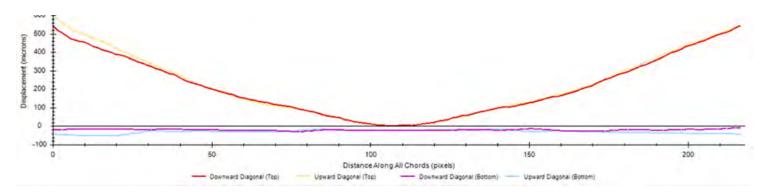

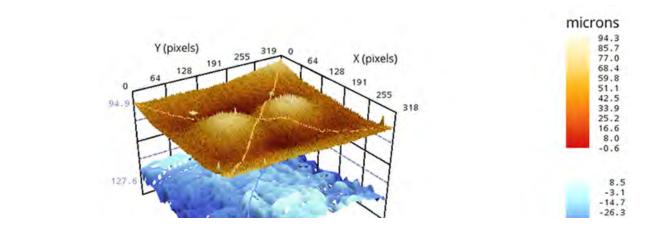

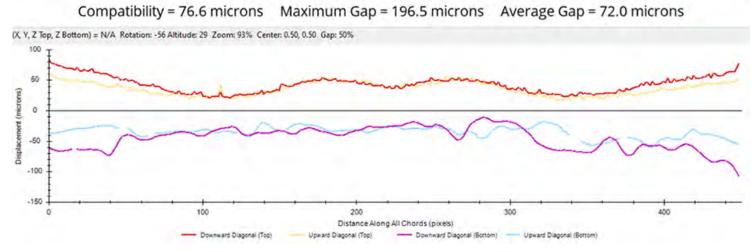

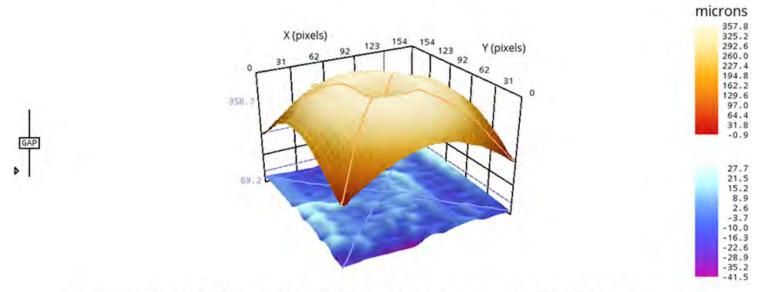

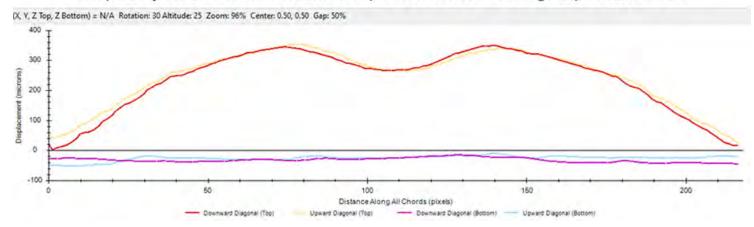

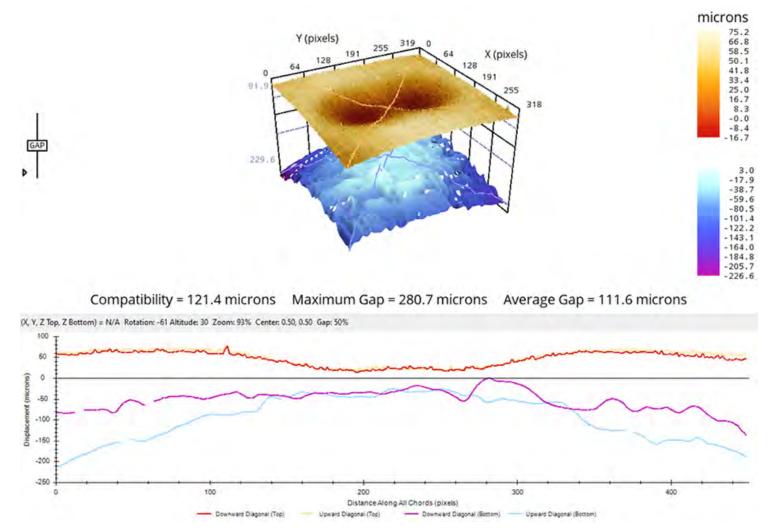

#### Selectively Assembling High-Value Components Based on Warpage in Order to Improve Reliability

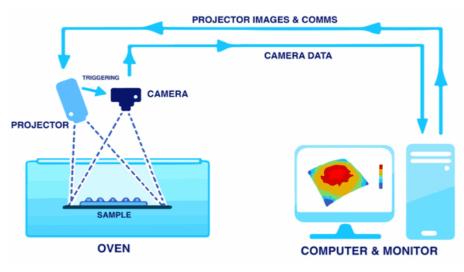

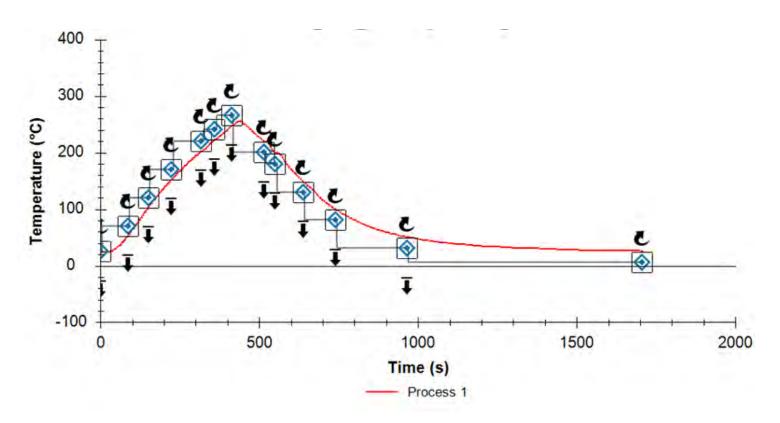

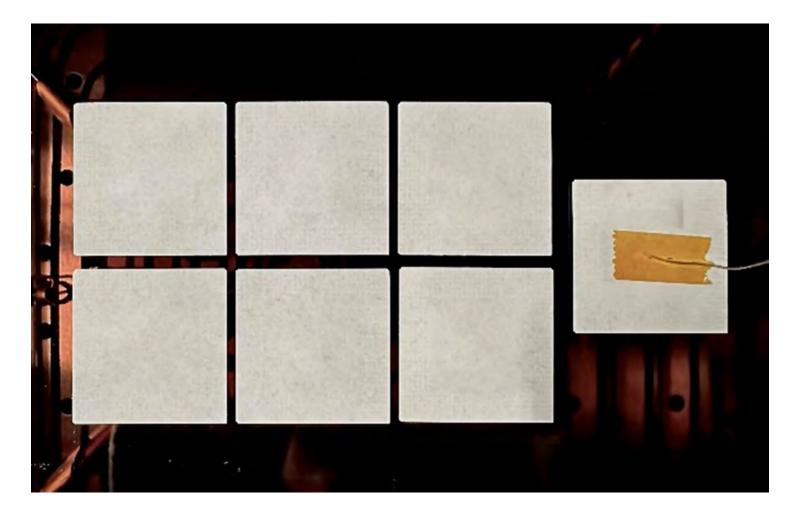

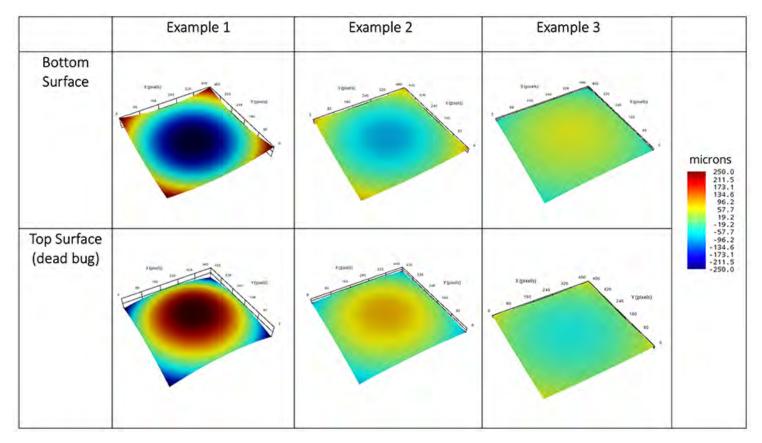

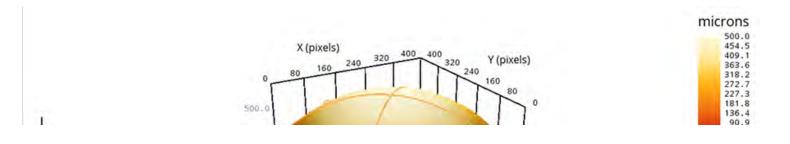

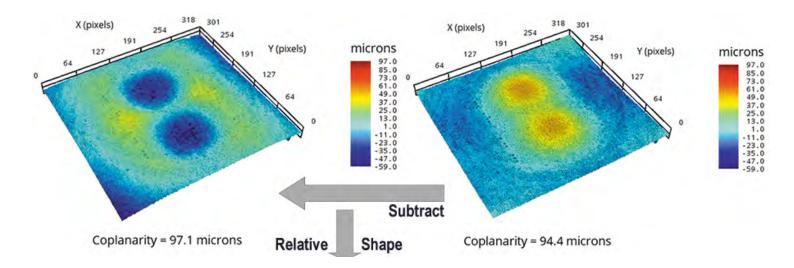

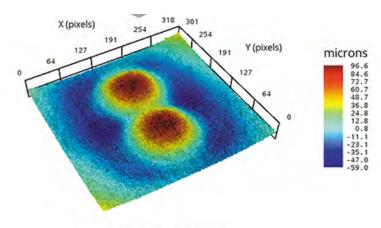

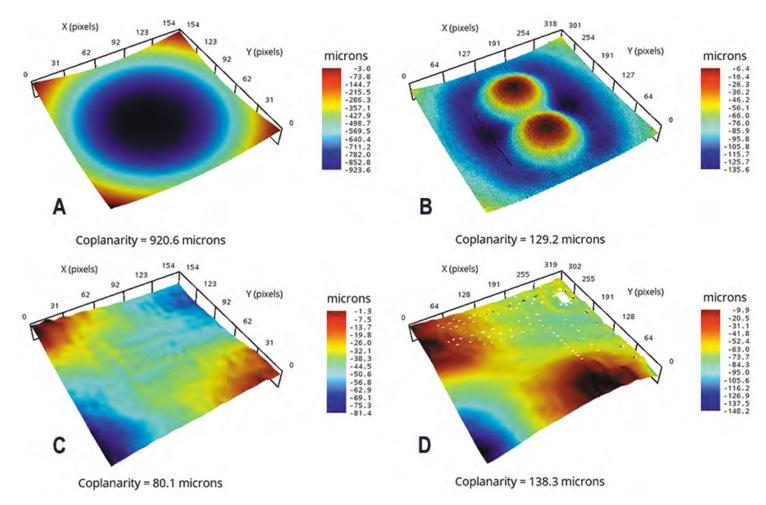

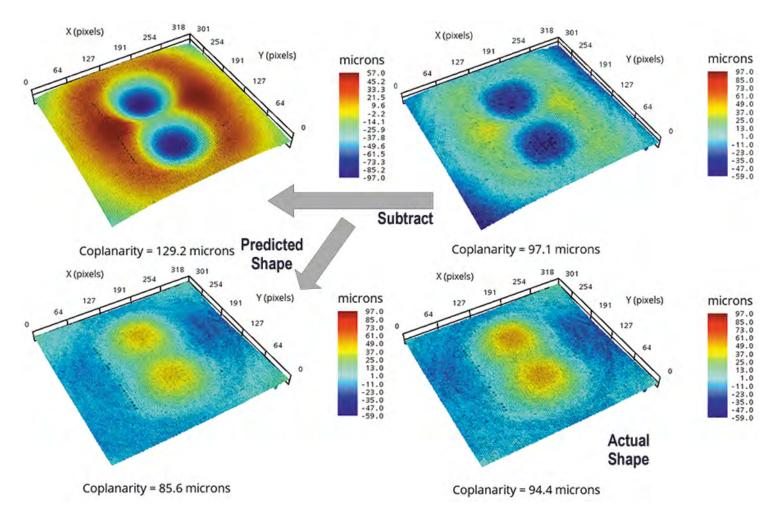

Surface warpage, or flatness, is an established source of reliability issues in surface mount devices, particularly when these surfaces are considered as they warp due to heat generated in production or real-world use. While measuring samples for thermal warpage is a common practice, an experimental concept is presented based on measuring warpage on SMD devices and the PCB landing areas where they would attach in assembly, then deciding which sample to place on which PCB. **by NEIL HUBBLE and CHANCE RABUN**

#### LEGISLATION

#### Public Sector Efforts 'Chip Away' at PCB Funding Deficit

The PCBAA is ramping up efforts to secure funding for R&D and capacity in the US. PCBAA executive director David Schild explains. **by MIKE BUETOW**

#### ON PCB CHAT (PCBCHAT.COM)

EDA SOFTWARE MARKET UPDATE with WALLY RHINES

#### THERMAL INTERFACE MATERIALS

with CLAIRE WEMP, PH.D.

HIGHLY ACCELERATED LIFE TESTING (HALT)

with DR. CHRISTOPHER JACKSON

US PCB INDUSTRY LEGISLATION UPDATE

with DAVID SCHILD

#### FIRST PERSON

THE ROUTE Blast from the past. Mike Buetow

#### MONEY MATTERS

ROI More data are not always best. Peter Bigelow

FOCUS ON BUSINESS Prepping for OEM movement. Susan Mucha

#### TECH TALK

DESIGNER'S NOTEBOOK A roadmap of the future. John Burkhert, Jr.

DESIGN BEST PRACTICES Managing library and design data. Stephen Chavez

#### MATERIAL GAINS Adaptability is the key to growth.

Alun Morgan

#### THE FLEXPERTS

Copper or CuNi? Mark Finstad

**SCREEN PRINTING**

Less than you bargained for. Clive Ashmore

#### **TECHNICAL ABSTRACTS**

#### DEPARTMENTS

AROUND THE WORLD PCEA CURRENT EVENTS MARKET WATCH OFF THE SHELF

### Measure PCB Surface Finishes ENIG, EPIG, EPAG & ENEPIG

X ....

- XRF with Automated X-Y Table

- Increased Throughput

- Improved Reliability

- IPC 4552 B & IPC 4556

Measuring Made Easy®

www.fischer-technology.com | info@fischer-technology.com | 860.683.0781

PCEA PO BOX 807 AMESBURY, MA 01913

#### PCEA BOARD OF DIRECTORS

Stephen Chavez, CHAIRMAN Justin Fleming, SECRETARY Gary Ferrari, CHAIRMAN EMERITUS

#### **MEMBERS**

**Michael Buetow** Tomas Chester Michael Creeden Douglas Dixon **Richard Hartley** Scott McCurdy Anaya Vardya Susy Webb Eriko Yamato

#### PCEA.NET

#### THE PRINTED CIRCUIT ENGINEERING ASSOCIATION, INC. BRANDS:

| PUBLICATION                |                              |

|----------------------------|------------------------------|

| PCD&F/Circuits Assembly    | digital.pcea.net             |

| WEBSITES                   |                              |

| PCD&F                      | pcdandf.com                  |

| Circuits Assembly          |                              |

| NEWSLETTER                 |                              |

| PCB Update                 | pcbupdate.com                |

| PODCASTS                   |                              |

| PCB Chat                   | pcbchat.com                  |

| EVENTS                     |                              |

| PCB West                   | pcbwest.com                  |

| PCB East                   | pcbeast.com                  |

| EDUCATION                  |                              |

| PCB2Day                    | pcb2day.com                  |

| Printed Circuit University | printedcircuituniversity.com |

| AWARDS PROGRAMS            |                              |

| Service Excellence Awards  | circuitsassembly.com         |

| NPI Awards                 | circuitsassembly.com         |

|                            | pcdandf.com                  |

| DATABASE                   |                              |

| Directory of EMS Companies | circuitsassembly.com         |

PRINTED CIRCU DESIGN & FA pcdandf.com circuitsassembly.com

#### STAFF

#### PRESIDENT

Mike Buetow 617-327-4702 | mike@pcea.net VICE PRESIDENT, SALES & MARKETING

Frances Stewart 678-817-1286 | frances@pcea.net

SENIOR SALES EXECUTIVE Brooke Anglin 404-316-9018 | brooke@pcea.net MANAGING EDITOR Tyler Hanes 205-258-0067 | tyler@pcea.nett

#### PCD&F/CIRCUITS ASSEMBLY EDITORIAL

MANAGING EDITOR

Tyler Hanes 205-258-0067 | tyler@pcea.net

#### COLUMNISTS AND ADVISORS

Clive Ashmore, Peter Bigelow, Robert Boguski, John D. Borneman, John Burkhert, Jr., Stephen Chavez, Joseph Fama, Geoffrey Hazelett, Mark Finstad, Nick Koop, Geoffrey Leeds, Alun Morgan, Susan Mucha, Greg Papandrew, Chrys Shea, Jan Vardaman, Gene Weiner

#### PRODUCTION

**ART DIRECTOR & PRODUCTION** blueprint4MARKETING, Inc. | production@pcea.net

#### SALES

VICE PRESIDENT, SALES & MARKETING Frances Stewart 678-817-1286 | frances@pcea.net

SENIOR SALES EXECUTIVE Brooke Anglin 404-316-9018 | brooke@pcea.net

#### REPRINTS

brooke@pcea.net

#### **EVENTS/TRADE SHOWS**

EXHIBIT SALES

Frances Stewart 678-817-1286 | frances@pcea.net

**TECHNICAL CONFERENCE**

Mike Buetow 617-327-4702 | mike@pcea.net

#### SUBSCRIPTIONS

PRINTED CIRCUIT DESIGN & FAB/CIRCUITS ASSEMBLY is distributed without charge to qualified subscribers. To subscribe, visit pcdandf.com or circuitsassembly. com and click on Subscribe. For changes or cancellations to existing subscriptions: subscriptions@pcea.net

PRINTED CIRCUIT DESIGN & FAB/CIRCUITS ASSEMBLY is published monthly by Printed Circuit Engineering Association, Inc., PO Box 807 Amesbury, MA 01913. ISSN 1939-5442. GST 124513185/ Agreement #1419617.

© 2023, Printed Circuit Engineering Association, Inc. All rights reserved. Reproduction of material appearing in PRINTED CIRCUIT DESIGN & FAB/ CIRCUITS ASSEMBLY is forbidden without written permission.

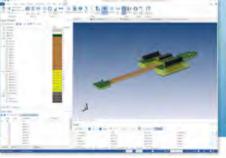

### Support For Flex, Rigid Flex and Embedded Component Designs Now Available.

DownStream's CAM350 and BluePrint-PCB support importation and visualization of PCB designs containing Flex, Rigid Flex or Embedded components. Visualize designs in both 2D and 3D, and easily document complex Flex or Rigid- Flex Stack-Ups for submission to PCB Fabricators.

- Import and Visualize Flex, Rigid-Flex and Embedded Component Designs

- 3D Visualization to Validate PCB Construction and Component Assembly

- Manage Variable Stackup Zones for Rigid-Flex Designs

- Easily Create Custom Flex or Rigid-Flex Fabrication and Assembly Documentation

- Use DFM analysis to analyze a flex or rigid-flex design for potential fabrication or bend related defects

Use Stack Up Visualizer and Blueprint's Rigid-Flex Stackup template to easily manage and document rigid-flex stackups.

A rigid-flex design in 3D. Shown with layers spread to improve visualization of the layer stackup. Use Rigid-Flex and Inter-layer DFM analysis to analyze flex and rigid-flex designs.

For more information visit downstreamtech.com or call (508) 970-0670

### The '80s Revival

IN A BLAST from the past, Marc Carter, one of the leading proponents of integrating electronics design and manufacturing technical skills into the educational system, shared a review of the Nepcon West trade show written by the LA Times ... in 1986. The flashback is priceless.

Most readers won't remember Nepcon, but it was the giant of that and any era when it came to electronics manufacturing. It would draw 30,000 to 40,000 engineers and other industry professionals to Anaheim, CA, each February to peruse the 1,000 or so exhibitors from all over the world. It was truly staggering.

The review Carter shared dwelled on surface mount equipment, which was just getting going in the US at the time. (Phil Marcoux, one of PCEA's advisors, is credited with installing the first such line in the US while running an EMS called AWI in the early 1980s. One of the first SMT boards I've seen – or even know of – was used in the early Saturn rockets now on display at the US Space and Rocket Center in Huntsville, AL, and is featured on this month's cover photo.) Most assembly process equipment then, however, was either through-hole or, if SMT, it was semiautomatic, a far cry from the robot- and software-intensive Industry 4.0-run factories in some regions today.

Per the article, about 10% of US manufacturers and 30% of their Japanese counterparts were using SMT at the time, with penetration in Europe nestled somewhere between the two regions.

Perhaps the most stunning change between then and now is the demographics. Attendees from offshore, including one quoted from Nan Ya, walked Nepcon looking for equipment not available in the Pac Rim. The US should be so lucky now.

One prescient manufacturer's representative said this: "The boom days (for electronics) are over. Opportunities are going to have to be sought out and developed." (Do you agree?)

Joe Fjelstad, he of more than 200 patents in flex circuits and packaging – and countless more pending – is one who continues to try to seek and develop those opportunities. I've been hearing the words "Fjelstad" and "guru" for so long, I was stunned when I learned he's not much older than me.

A few months back I challenged Fjelstad to consider what ideas were conceived and discarded years or decades ago but might be relevant today. He returned to us our cover story this month, which investigates the unstructured evolution of integrated circuit package technology – and its consequences.

The article is a few clicks away and I'm not going to summarize it here. Rather, it's the side conversations that led up to the contribution that I want to share.

Fjelstad's mind is comprehensive and frighteningly dynamic, and conversations with him inevitably wander into all sorts of unexpected and neat areas.

Among other things, we talked about the renaissance of polymer thick film, for instance, a technology some four-decades-old that the US government is investing tens of millions in today. And we covered the seismic geographical shifts that took place, in some cases almost by accident.

To wit: Back in the 1980s and early 1990s, the consensus was Japan's investments in miniaturization coupled with its patience and long-range strategic thinking (remember the 100-year plan?) and superior marketing skills were going to dominate the electronics industry forever. Never underestimate those key decision points. Japan missed on array packaging, opening the door to geographical competition. (I should mention, the US and European bare board industries did something similar in the late 1990s and early 2000s, focusing almost exclusively on high-layer-count boards at the expense of HDI. And while it's understandable why they did so at the time – order backlogs were pushing nine to 12 months – in retrospect that was a very big miss.)

One of the side effects of economic recessions and the race to lower-cost builds is the loss of a few more of the (already few) remaining seers. "We lose the dreamers, the imagination," Fjelstad says.

We contemplated this ongoing conundrum of the industry today, which is that we are surrounded by great engineers, but they are tasked with improving what already exists.

So many new inventions come from outside the industry and get adapted for ours. As Fjelstad says, engineers today aren't given the freedom and challenge to ask, "How do I make this disappear in favor of something that doesn't even exist?"

We are ready for a new generation of architects, but where are they and, more importantly, who are they?

Assuming, of course, they are human and not ChatGPT-driven, we need look no further than our own conference and exhibition, PCB West, which takes place next month at the Santa Clara (CA) Convention Center. Our free sessions on Sept. 20, the same day as the exhibition, include presentations on developments that are expected within the next three years and their projected impact on the hardware and PCB engineering. These include development/convergence of AI, regenerative design, Mod-Sim and model-based systems engineering (MSBE). We could be on the cusp of a world with no netlists, highly automated data search and automated routing development that were the stuff of daydreams just a few years ago.

Nepcon West might be gone and (almost) forgotten, but the opportunities to be sought out and developed are staring right at us. Don't miss them.

mon

mike@pcea.net @mikebuetow

MIKE BUETOW is president of PCEA (pcea.net); mike@pcea.net.

## DESIGN DATA CONFIDENCE, NOT CONFUSION

#### WHAT CAN DATA MANAGEMENT DO FOR YOU?

Bring your data into one shared space directly in OrCAD. Stay connected with a streamlined, collaborative approach to PCB Design.

### American Standard Circuits Acquires Sunstone Circuits

WEST CHICAGO, IL – American Standard Circuits and Sunstone Circuits in July announced a merger of their respective printed circuit board fabrication operations.

Terms of the deal between the two privately held manufacturers were not disclosed, but all current operations will be maintained, the companies said. Matt Stevenson, who has been with Sunstone more than 17 years, has been named vice president and general manager of the merged entity, ASC Sunstone Circuits.

In a statement, the companies called the deal a "strategic alliance [that] brings numerous advantages to customers."

"Together, we bring an unmatched combination of expertise, capabilities and resources to our customers," said Anaya Vardya, CEO, American Standard Circuits, in a statement. "This merger will enable us to deliver greater value, innovation and responsiveness, solidifying our position as the premier PCB manufacturing partner."

The combined firms will offer a broad range of PCB types, materials, and certifications, including single-sided, double-sided, multilayer, RF/microwave, flex/rigid-flex, HDI, ultra HDI, and metal-backed boards.

Sunstone Circuits will continue to offer its quickturn prototype and low-volume services, while ASC, which has multiple operations, provides higher-volume runs.

"The acquisition is complementary," Vardya elaborated in an interview with PCD&F/CIRCUITS

ASSEMBLY. "Sunstone does a lot of quickturn. ASC has many outlets for the follow-on production," citing facilities in West Chicago and overseas.

There is "virtually no overlap of customers," he added.

The addition of Sunstone, which is capable of accelerated prototyping (24-48hr.) and operates outside Portland, OR, gives ASC factories in the US Central and Pacific time zones, plus overseas.

Sunstone will maintain its dynamic online PCB quoting options and automated front-end design and engineering tools. Customers now have access to a comprehensive and user-friendly design software solution that includes powerful tools for schematic capture, PCB layout and integrated parts library, the companies said.

Sunstone's longstanding relationship with Screaming Circuits will continue post-merger, while its customers will now have access to ASC's global sourcing division and network of partners and suppliers of components, materials, and manufacturing services from various locations globally.

"We have customers that require a total solution," Vardya said. "We always wanted to be a total solution for customers."

Terry Heilman, CEO, Sunstone Circuits, added: "This merger represents a transformative opportunity for our customers. By leveraging the strengths of both companies, we are positioned to provide a comprehensive range of PCB solutions and deliver unparalleled customer experiences. We are excited to embark on this journey together."

Heilman and Sunstone Vice President and COO Rocky Catt will remain with the merged entity for an unspecified period.

One of the older PCB fabricators in the US, Mulino, OR-based Sunstone was founded in 1972 and has 104 employees. American Standard Circuits was founded in 1988.

Vardya said ASC will "continue to look" for other acquisitions. "Our plan is to grow organically and through acquisition. It's one reason we aligned with private equity a few years ago." **EP**

### Ansys and Altium to Connect ECAD,

### Simulation Tools

PITTSBURGH – Altium and Ansys are partnering to improve the electronic design and development process by digitally connecting Altium's electronic computer-aided design (ECAD) tools and Ansys Electronics Desktop.

The integration, set to be available in the second half of 2023, is meant to create a new level of digital continuity while helping to reduce development time and the risk of design errors, the companies said in a release.

The companies said the connection will facilitate seamless collaboration, streamlining the exchange of design data and enabling engineers to work together more effectively within a fully integrated workflow. By eliminating the need for import/export translations and replacing manual, ad-hoc communication methods, the integration supports predictive accuracy, synchronization, and productivity, while reducing the risk of errors. As a result, the digital bridge also minimizes the potential for respins and delays.

"As companies innovate to meet the demand of today's competitive landscape, they face new product complexities and engineering challenges that require extensive cross-domain collaboration and advanced simulations. And the outdated, manual integration methods being utilized are holding them back," said Tomek Brzuchacz, head of CAD software at Altium. "This digital connection between ECAD and simulation enables electrical engineers and simulation engineers to work together with ease and accuracy, helping companies to accelerate design time and minimize additional costs."

"Electronics designers and engineers work tirelessly to produce the countless connected devices and applications demanded by today's market, and it is critical to equip these innovators with the same level of connectivity during design and development," said John Lee, vice president of the electronics, semiconductor and optics business unit at Ansys. "With a bidirectional link between Ansys and Altium solutions, electrical engineers will no longer be slowed down or interrupted by data communication and can focus on design, innovation and collaboration."

### SEL Hosts Ribbon-Cutting for New PCB

### Factory

MOSCOW, ID – Schweitzer Engineering Laboratories hosted a ribbon-cutting ceremony for its new printed circuit board factory here on Jun. 28.

The 162,000 sq. ft. facility houses the operation to fabricate the printed circuit boards used in its products that protect, monitor, control and automate electric power systems around the world. The facility is expected to employ around 60 people, with positions ranging from a variety of engineering roles, including chemical, mechanical, software and computer-aided manufacturing to equipment operators and maintenance workers.

Construction on the facility began in spring 2021. 🚝 P

### ECIA Releases New Component Training Modules

ATLANTA – ECIA Foundation announced the release of the second stage of its e-learning modules for teaching the basics of the electronic components industry to new employees.

Phase II of the members-only PACE training program consists of five new courses covering the following topics:

- Supply Chain Management: The Hidden Value of Distributors

- Establishing the Distribution Strategy: Supplier Needs vs. Customer Wants

- CRM, ERP and More: The Platforms Powering the Digital Supply Chain

- Demystifying Sales: Pricing, Roles and More

- Driving the Future with Electronics: Evolving Industries and Applications

ECIA developed the introductory five courses and an interactive platform with Lectrix Group, a sales strategy and marketing group. Since its launch in May 2022, the program has seen more than 1,000 learners and received positive reviews.

"The response to this program has far exceeded our expectations," said David Loftus, president and CEO, ECIA. "It was intended to capture and underline the importance of the channel to the broader tech industry. This curriculum provides the next generation of electronic component industry champions a baseline working knowledge of our industry, and that will help attract and retain the talent that is so essential to our member companies."

Phase I courses cover the basics of the electronic component channel and includes these topics:

- An Introduction to the Electronics Industry: Manufacturers, Independent Manufacturers' Representatives, and Distributors

- The Supporting Industry Partners

- Taking a Product to Market: How a Component Manufacturer Launches a New Product

- An Introduction to Basic Electronic Components

- Electronics Industry Terms and Conditions

Member companies can gain access to the training by creating a profile on the ECIA website and then visiting ecianow.org/PACE.

### US Outlines CHIPS Act Funding Opportunities

WASHINGTON – The US Department of Commerce in late June announced an expansion in funding opportunities for large semiconductor supply chain projects, as well as a separate process for smaller projects coming later in the year.

As part of the CHIPS and Science Act, the Department of Commerce is overseeing more than \$50 billion to revitalize the US semiconductor industry, including \$39 billion in semiconductor manufacturing incentives. The first funding opportunity seeks applications for projects to construct, expand or modernize commercial facilities that produce leading-edge, current-generation and mature-node semiconductors.

This same funding opportunity is now open to materials and manufacturing equipment facility

projects with capital investments equal to or exceeding \$300 million.

Large-scale supply chain projects that are now eligible will follow the five-part application process laid out in the first funding opportunity: statement of interest, pre-application (optional but recommended), full application, due diligence and award preparation and issuance. Applicants will be evaluated based primarily on the extent to which the application addresses the program's economic and national security objectives, but they will also be evaluated based on commercial viability, financial strength, project technical feasibility and readiness, workforce development, and broader impacts.

An additional funding opportunity will be released in the fall for supplier projects below the \$300 million threshold with a tailored application that smaller businesses can navigate.

"After the pandemic exposed holes and bottlenecks in our semiconductor supply chains that sent shockwaves across our economy, the CHIPS and Science Act is a historic opportunity to ensure our microchip supply chain resilience," said US Secretary of Commerce Gina Raimondo. "Thanks to President Biden's Investing in America agenda, we're already seeing billions in private sector investment bolster the semiconductor supply chain. We're laying out our vision for how we'll build on that progress by responsibly making investments to ensure resiliency and success for the clusters we will create."

Alongside the funding opportunity for larger supply chain projects, the Commerce Department also released a "Vision for Success" outlining strategic objectives for investments in the semiconductor supply chain. The goals in the vision paper include: 1) strengthening supply chain resilience, including by reducing chokepoint risks flowing from the geographic concentration of critical semiconductor inputs; 2) advancing US technology leadership, including by incentivizing major US manufacturing equipment and materials suppliers to increase their footprints in the United States and attracting non-US suppliers of the world's most advanced equipment, materials, and subsystems to establish large-scale footprints in the US; and 3) supporting vibrant US fab clusters, including by ensuring that each CHIPS-funded cluster is supported by an ecosystem of reliable suppliers.

### Arkema to Acquire Controlling Stake in PIAM

COLOMBES, FRANCE – Arkema will acquire a 54% stake in South Korean polyimide film producer PI Advanced Materials for €728 million (\$791 million).

PIAM had sales of more than  $\in$ 200 million in 2022, and expects sales to grow 13% per year, driven by demand for polyimide in lithium-ion batteries, 5G antennas, high-resolution OLED displays or flexible screens, and supported by recent capacity expansions.

The transaction will be fully financed in cash, and after approval by Chinese and Korean antitrust authorities, should be finalized by the end of 2023, Arkema said.

"PIAM is an outstanding company with a unique technological positioning, state-of-the-art manufacturing facilities and invaluable customer relationships," said Thierry Le Henaff, chairman and CEO, Arkema. "This acquisition is fully aligned with our strategy to be at the forefront of highperformance materials for high growth end markets supported by megatrends such as electric vehicles and advanced electronics.

"After the divestment of PMMA, the acquisition of Ashland adhesives and the current start-up of our bio PA11 plant in Singapore, Arkema is delivering another significant milestone of its strategy focused on innovative materials for a sustainable world," said Le Henaff.

With two production sites and two R&D centers in South Korea, PIAM employs approximately 320 people. **=P**

### NI Stockholders Approve \$8B Emerson Merger

AUSTIN, TX – National Instruments stockholders approved the company's acquisition by Emerson Electric during a special meeting in June, with stockholders receiving \$60 per share in cash for every share of NI common stock they own.

The \$8.2 billion merger agreement was first announced by Emerson earlier this April.

"Today's vote by our stockholders validates our belief that this transaction represents the best outcome for all NI stakeholders," said Eric Starkloff, CEO, NI. "We thank our stockholders for their support and look forward to accelerating our position as a leading provider of software-connected automated test and measurement systems in this next chapter as part of Emerson."

The proposed transaction is expected to close in the first half of Emerson's fiscal year 2024, subject to the completion of customary closing conditions.

### Technoprobe to Acquire Harbor Electronics

MERATE, ITALY – Technoprobe, an Italian manufacturer of chip testing solutions, signed a binding offer in July to acquire California-based PCB maker Harbor Electronics.

Under the terms of the offer, which includes a 30-day exclusivity period to finalize and sign the final acquisition agreement, Technoprobe will pay around \$50 million net of any adjustments related to changes in the target company's cash holdings.

Harbor Electronics, founded in the 1980s in Santa Clara, CA, and acquired in 2015 by the Shenzhenheadquartered Fastprint Circuit Tech group, is a manufacturer of advanced PCBs for testing systems for major semiconductor manufacturers. Last year, the company reported revenues of around \$52 million, an EBITDA of about 16%, and a net financial position of about \$5 million.

With the acquisition, Technoprobe will further strengthen its technological competencies in the testing area by vertically integrating its production process through the in-house production of advanced printed circuit boards for its probe cards and final test boards, the company said in a release.

"The acquisition of Harbor Electronics has an important strategic value because it allows us to consolidate the process of vertical integration of the production process of our probe cards by leveraging the significant technological synergies of two important players in the testing field," said Technoprobe CEO Stefano Felici. "In addition, the distinctive skills of Harbor Electronics will allow us to increase our knowledge in the final testing segment."

### Amara Raja Electronics Acquires Stake in Design Alpha

CHITTOOR, INDIA – Amara Raja Electronics announced the acquisition of a stake in engineering design firm Design Alpha. The acquisition will position Amara Raja Electronics (AREL) as a fully integrated electronics systems design and manufacturing (ESDM) company, unlocking numerous opportunities in the electronics manufacturing business, the company said in a statement.

Based in Kochi, India, Design Alpha specializes in supporting deep science and engineering development by offering design expertise and services. AREL did not disclose the percentage of shares it acquired.

Besides opening doors to partnerships with large multinational corporations and expanding their customer base, the acquisition will also facilitate seamless integration of design and manufacturing processes, along with the provision of value-added services to enhance product performance, efficiency, and reduce time to market, the company said.

"The acquisition will accelerate product development for AREL and allow us to leverage specialist knowledge," said AREL director Vikramadithya Gourineni. 🚝 🏳

### Congressman Visits Pro-Tech Interconnect Solutions

CHASKA, MN – PCB manufacturer Pro-Tech Interconnect Solutions recently hosted a tour of its facility here by Rep. Tom Emmer.

Pro-Tech's Chaska facility has 83 employees and manufactures PCBs for the military, aerospace, medical and commercial industries.

"Manufacturing products like chips and semiconductors here at home doesn't just provide goodpaying jobs to Minnesotans. Investing in the production of this essential technology is important to our national security," Emmer said. "Thank you to the team at Pro-Tech for sharing their work with us."

"Pro-Tech Interconnect Solutions LLC is the only 100% woman-owned and operated "rigid" printed circuit board manufacturer in the USA," said Pro-Tech President Melanie Bera Anderson. "We build boards for the F-35 jet, medical implants and equipment, to commercial controls."

Pro-Tech was founded in 1968, and since 2018 has been operated by American Circuit Corp. 🚝 P

### IPC: European Electronics Industry Needs Further Support from EU

BRUSSELS, BELGIUM – Key segments of the European electronics manufacturing industry face significant challenges and require more support, according to a new report from IPC.

The report says the recently enacted European Chips Act is a welcome step, but "the near singular focus" on the semiconductor industry "has obscured critically important segments of the electronics ecosystem," specifically printed circuit boards and electronic assembly, without which semiconductors cannot function.

Over the past 20 years, the European PCB sector experienced a steep decline, the report says, shrinking from approximately 20-30% of global production to just 2% today. Over this time, the EU has become "highly dependent on China," which now accounts for some 65% of total EU PCB requirements.

The EMS sector has experienced "solid" average annual growth in recent years, fueled by factory investment by large global companies and by the growth of the downstream markets the sector serves, including automotive, industrial, aerospace, defense, and healthcare. However, the EU imports roughly 90% of required EMS products and services.

The European Commission is continuing to examine vulnerabilities in its industrial supply chains. In June, the European Commission's Directorate General for Internal Market, Industry, Entrepreneurship and SMEs (DG GROW) hosted a meeting on electronics assembly and printed circuit board manufacturing with key industry stakeholders, including companies from the renewable energy, aerospace/defense, automotive, and industrial sectors. The structured dialogue was called on the heels of an IPC meeting in April that brought together leaders of government and industry to press for an EU strategy to strengthen silicon-to-systems innovation and manufacturing.

### USI Opens Second Factory in Poland

KOBIERZYCE, POLAND – Universal Scientific Industrial inaugurated its second factory here in June, and expects to create up to 1,000 jobs once the facility is fully operational by the first quarter of 2024.

"This new plant will strengthen our manufacturing capabilities and enable us to meet the growing demand for electric vehicle and green energy solutions in the European market," said senior vice president Brian Shih, USI.

USI is a subsidiary of ASE Technology and parent company of AsteelFlash.

"Today we are proud to create a milestone for USI/AsteelFlash customer service," said Felix Timmermann, executive director of USI Poland and executive vice president of Asteelflash. "We are strengthening our readiness to support our customers' manufacturing and relocation efforts and ensuring that we are doing the best we can for our customers. We are convinced that this new activity will unleash our potential here and will be the start of something big."

"We hope that the presence of such an important investor for the industry as USI, and its direct association with the Taiwanese ASE Technology, will attract new investments in Poland and contribute to the development of the electronics and semiconductor industries, sectors for the Polish, European and global economies," said Marcin Fabianowicz, head of direct investments in Poland as managing director of the Polish Investment and Trade Agency.

### GPV to Open 3rd Factory in Slovakia

PIESTANY, SLOVAKIA – GPV has entered a lease agreement for a new electronics factory here near its two existing factories in Slovakia. The additional factory is expected to start production from early 2024.

The new factory comprises a total of 18,000 sq. m., and the company will initially use 11,000 sq. m. with the option to expand and use the additional space at a later stage if needed.

In a release announcing the move, GPV said customers have been requesting additional production capacity in Europe, and after GPV's merger with Enics in October 2022, the company managed to expand production capacity to better accommodate customer needs in the short time while continuing to look for a possibility to establish additional production capacity in Europe.

"With the additional space in Slovakia, we will have an even stronger operational footprint in bestcost Europe. We have a strong pipeline driven by increased demand from satisfied customers and we have a strategic ambition to regionalize European demand also in the light of the ESG agendas. Furthermore, we experience a big appetite toward best-cost Europe from existing and new potential customers, who wish to be served close to their core markets," said Bo Lybæk, CEO, GPV.

The company said the additional factory will strengthen its site profile to respond with the requirements from the European core regions, and it will pave the road to support growth in the coming years.

"We expect to be able to combine the strengths from our 19 existing operating business units to further increase our competitiveness in the high-mix EMS market. I look forward to following the process, and I see this as an important strategic step in strengthening our operational footprint to serve our customers even better," Lybæk said.

### Scientists Develop Technology to Quickly 3-D Print Flexible Smart Devices

SINGAPORE – Scientists from Nanyang Technological University, Panasonic and Singapore Center for 3-D Printing have developed a new multi-material printer using multi-wavelength highpower lasers for quick and easy 3-D printing of smart, flexible devices.

The multi-material printer works by utilizing varying wavelengths of laser, creating thermal and chemical reactions capable of transforming common carbon-based materials (polyimide and graphene oxide) into a new type of highly porous graphene. The resulting structure printed with this new graphene is not only light and conductive, but it can also be printed or coated onto flexible substrates like plastics, glass, gold and fabrics, creating flexible devices.

Electronic devices and components have traditionally been made of rigid materials such as metals, silicon, and ceramics, but there has been an increasing interest in the creation of flexible wearable electronics that can be bent, twisted, and easily conformed to various surfaces.

"Our project aims to find a way to 3-D print new materials like organic polymers and carbon-based materials like graphene, which has properties that allow them to be printed or coated onto flexible

substrates like plastics or fabrics, creating flexible and stretchable circuits," said project co-leader Murukeshan Vadakke Matham, an associate professor from NTU School of Mechanical and Aerospace Engineering (MAE) and SC3DP, the national center of excellence in 3-D printing housed at NTU.

"3-D printed flexible electronics paves the way for more comfortable and mobile wearable devices as it can be lighter and smaller," added Murukeshan, who is also principal investigator at Singapore's National Additive Manufacturing Innovation Cluster (NAMIC). "We can now create unique structures that were previously impossible with traditional rigid electronics."

The newly created 3-D printer has already attracted interest from various companies, including American multinational manufacturer Jabil-MTI Penang.

Jabil-MTI Penang aims to integrate 3-D printed graphene-based electronics into a smart infusion system. A proof of concept has been demonstrated through a prototype of a low-cost intravenous (IV) fluid bag with an embedded printed sensor powered by artificial intelligence. The device monitors the status of the IV drip, regulates parameters such as pressure flow and temperature, and transmits the information to a smartphone in real-time. This allows medical personnel to remotely monitor, control and detect abnormalities efficiently.

The research team also tested the possibility of integrating 3-D printed components into the fabrication of high-performing electronics like pressure sensors and heaters.

"We greatly value NTU and Panasonic teams' creative thinking and innovative approach, and we are excited about the possibilities for future collaborations," said Jabil-MTI Penang project manager Lim Lai Ming. "We eagerly look forward to exploring further opportunities to work together and leverage both their teams' exceptional innovation expertise."

"Our technology allows the creation of highly porous and conductive graphene-based material for use in different applications," said project co-leader Dr. Low Mun Ji, general manager of Panasonic. "Compared to traditional graphene manufacturing methods, our method is faster, cheaper, and highly compatible with a wide range of materials."

### Incap Acquires US-based Pennatronics

HELSINKI – Incap has gained a foothold in the US with the acquisition of the Pennsylvania-based EMS company Pennatronics in a cash and stock transaction.

The enterprise value of the acquired company is \$18.6 million, and the agreement also includes a potential additional earn-out of a maximum of \$3 million. The transaction will be paid in cash except for the amount of approximately \$1.6 million which will be paid in Incap's shares.

Pennatronics has 102 employees working out of a 6,000 sq. m. production facility near Pittsburgh, PA, and offers complete electronics manufacturing services including PCB assembly and box-build assembly, as well as engineering and sourcing services. The company saw \$30 million in revenue in its last financial year, and its EBITDA was \$2.9 million.

Incap said the acquisition is in line with its growth strategy and will establish Incap's presence in the US market and create a foothold for further expansion in the country. Pennatronics' US production facility complements Incap's current production facilities located in Estonia, India, the UK and Slovakia.

The company said the acquisition will broaden Incap's customer base and will allow for US-based services to be offered to existing and new customers while Pennatronics' customers will benefit from opportunities to source services from Europe and India, and in the long term, the acquisition is expected to bring cross-selling opportunities and synergy benefits.

"I am very excited about widening our geographic presence and gaining foothold in the US market," said Incap CEO Otto Pukk. "I am also very happy to welcome the Pennatronics team of 102 professionals onboard. The acquisition will benefit both companies' existing customers with opportunities to source from new areas and I am convinced that, together with Pennatronics, we can create new opportunities to expand our business in line with our growth strategy."

After the acquisition, the former owners of Pennatronics, Ralph B. Andy and Keith D. James, are committed to support Incap over the transition period.

"I am enthused about the opportunity for our seasoned management team and dedicated employees to join forces with Incap," said Andy, who serves as president and CEO. "The Pennatronics team is excited to become Incap's first factory and cornerstone facility in the US to help fuel their future growth. This combination will enable us to take our business to the next level and provide our customers with enhanced capabilities and even greater value. I wish Incap North America a

### Note Grows in UK With DVR Acquisition

STOCKHOLM – Note has expanded its manufacturing capacity in the UK with the acquisition of electronics manufacturer DVR. The EMS company will pay GBP9 million (\$11.4 million) in cash, plus potential earnouts of up to GBP3 million (\$3.8 million) based on future growth and profitability targets.

DVR is located in Basildon, Essex, and the British EMS market, which corresponds to the Scandinavian market in size, is expected to have clearly higher growth than the European EMS market in general, Note said in a release announcing the acquisition. Through the addition of a fourth plant in England, the company said it gains greater coverage and becomes a larger player in the growing British EMS market.

"Our business continues to develop strongly, and we are now making our third acquisition in the past year. We are very excited that DVR will now become part of the Note Group," said Note president and CEO Johannes Lind-Widestam. "The acquisition strengthens our position in the UK EMS market, which we strongly believe in and which is expected to have a strong growth in the coming years. DVR has a strong customer portfolio with exciting projects and we also see opportunities for synergies with our existing customers and suppliers. We look forward to continuing the profitable growth journey together with customers, staff and management at DVR."

DVR offers PCB and box-build manufacturing, with a substantial number of its customers in the industrial and greentech segments. The company was founded by the Hellings family and has been run and developed most recently under the leadership of David Hellings, who will continue his role as CEO of the company. The company has around 95 employees.

"I have come to appreciate Note as a company that shares our core values of long-term customer relationships and high quality in what we do," Hellings said. "We have many exciting customers and projects in our portfolio and see great advantages for both us and our customers to become part of a larger group and continue to develop our business together."

### Entech Expands in Australia and

### Malaysia

ADELAIDE, AUSTRALIA – Entech Electronics will expand in its native Australia and add its first plant in Malaysia, the EMS firm announced.

Entech, a contract manufacturer offering PCB assembly, turnkey assembly, prototyping, and bare PCB supply, has begun construction of a new Adelaide factory and HQ, with an anticipated move-in date of April 2024. The factory is being built on a 10,000 sq. m. site, with 4,500 sq. m. under cover, said Wayne Hoffman, CEO, Entech Group.

"It is a significant factory here in Adelaide ... with the capability to take our factory floor space to double what it is at the moment," he said.

The company said that continuous improvement, growth, and a focus on the global supply chain of electronics components and materials has also set the stage for its third manufacturing location and further expansion into Southeast Asia.

The company has a factory in Shenzhen, and has operated a Singapore supply hub for the past three years, reaching out to businesses in Malaysia in preparation for its latest overseas expansion.

Hoffman said the new Malaysian operation would feature "glue and screw operations" but also the full supply chain of plastics, metalwork, hardware, wiring and harnessing through to finished product.

### Critical Manufacturing Expands Operations into Mexico

**PORTO, PORTUGAL** – Critical Manufacturing has announced an expansion into Mexico to help meet the growing demands of American manufacturing systems. The new facility will serve as a strategic hub, fostering collaboration and innovation within the local manufacturing ecosystem, the company said.

As part of the expansion, the company named Juan Ledezma, an industry professional with a deep understanding of the Latin American market, general manager of Mexico. "Our expansion into Mexico marks a significant milestone for Critical Manufacturing," said Francisco Almada Lobo, CEO and cofounder. "With our strong foundation and a visionary leader like Juan Ledezma at the helm, we are poised to provide unparalleled support to our customers in Latin America and nearshore projects. We are excited to embark on this new chapter and contribute to the region's manufacturing excellence."

The ASMPT subsidiary provides a fully integrated, modular MES. The company said its decision to invest in Mexico aligns with its broader strategy of expanding its global footprint and fostering digitalization across international markets, and its commitment to providing localized support and expertise will enable Mexican manufacturers to accelerate their digital transformation journeys and achieve operational excellence.

"I am honored to lead the Mexico operations of Critical Manufacturing and contribute to the growth of the Latin American manufacturing industry," Ledezma said. "Our mission is to empower organizations to embrace digital transformation and realize the full potential of their manufacturing processes. We look forward to partnering with local businesses, driving innovation, and supporting our customers' success in this dynamic and evolving business environment."

### CMS Electronics Establishes Prototype-Focused Subsidiary

KLAGENFURT, AUSTRIA – CMS Electronics announced the expansion of its product portfolio with the establishment of a new subsidiary, PCBWhiz.

PCBWhiz utilizes an AI-assisted platform that provides instant quoting for prototype production. The software automatically analyzes specifications and extracts key technical parameters through its advanced algorithm. This enables immediate matching with the technical capabilities of production, as well as real-time checks on material availability and automated pricing of prototypes. Customers are presented with technical queries or alternative suggestions for components if material availability is insufficient, ensuring a seamless order process and timely initiation of production, and the price remains unchanged after the order is placed.

With the option to choose production locations in Europe or Asia (soon expanding to South America and Southeast Asia), PCBWhiz said it prioritizes data security and protection. All customer data generated through the platform is securely stored in Frankfurt, Germany, ensuring compliance with ISO27001 (Information Security Management System) and GDPR regulations.

"Our aim is to revolutionize prototype production through flexibility and applied technology/system in processing," said director Markus Quendler. "Our platform empowers customers to perform design for manufacturability (DfM) checks on their PCBs and analyze the bill of materials (BoM) for material availability and lifecycle status online 24/7 before placing an order."

CMS Electronics said the new subsidiary allows customers to benefit from the combined strengths of both companies and gain access to world-class prototyping solutions. The company said the move underscores its commitment to innovation and ensuring customers have access to the latest and most efficient technologies.

### Katek Completes Acquisition of Nextek

MUNICH – Katek SE announced that it has finalized the acquisition of Madison, AL-based electronics supplier Nextek. The acquisition, which was first announced last November, expands Katek's presence in North America and strengthens its industry presence in the fast-growing areas of homeland security and defense, medical technology, energy, high-end industrial, and aerospace, which is new for Katek, the company said in a release.

With around 160 employees and annual sales of more than \$43 million in 2022, Nextek is a developer of highly complex products for critical application areas, especially in the areas of prototyping and production of small to medium quantities and complements Katek Canada (formerly SigmaPoint) as a high-volume provider of complex electronics. Both companies benefit from the reshoring trend in North America, which is progressing massively due to the current economic and geopolitical tensions, Katek said.

In addition to quickturn prototype manufacturing, Nextek offers sophisticated PCBA and complete device construction (box-build) as well as analytical engineering, product engineering and extensive test services for its customers. Nextek is ISO 9001 certified and has obtained certifications and approvals in the field of aviation (AS 9100D), medical technology (ISO 13485) and military technology (ITAR registered), and has laboratory facilities for material testing and ensuring the required quality in critical application areas.

"The acquisition of Nextek is already our second pillar in North America. It not only enables us to serve our European customers local-to-local directly in the USA, but also opens up the opportunity for Katek to benefit from the generally strong growth trend in North America," said Katek CEO Rainer Koppitz. "With the relocation from Asia and the high investments in North America as well as in connection with the 'Inflation Reduction Act' of the American government, we are well positioned to achieve success. Nextek ideally complements our existing location in Canada in the field of high-value electronics and is already very profitable."

"Nextek is thrilled to be part of the Katek Group. We anticipate a successful integration and a bright future with great growth opportunities as part of Katek," said Nextek CEO John Roberts. "We look forward with excitement to tapping into the anticipated additional business potential on both sides of the Atlantic. Combined with the strength and capabilities of Katek Canada, we at Nextek see a very promising future for Katek in North America. The entire Nextek team can't wait to take the next steps together with Katek as part of 'TeamBlue."

### Kurtz Ersa Breaks Ground on Mexico Facility

JUÁREZ, MEXICO – Kurtz Ersa has broken ground on a new production facility here to meet the growing demands of the North America market.

The new plant will play a pivotal role in the production of Ersa soldering machines and will also serve as a preproduction center for Kurtz's US factory, the company said in a release. The expansion will create Kurtz Ersa's third-largest manufacturing site after Germany and China and will initially focus on manufacturing Ersa Hotflow reflow soldering systems.

"Mexico was chosen as the ideal location for this expansion due to its strategic advantages," said Albrecht Beck, Kurtz Ersa president and COO. "Its central location on the border provides excellent access and facilitates access to strong local markets in the Americas. Additionally, Mexico boasts a wealth of highly educated and motivated workforce to maintain our high German quality standards at a modern state-of-the-art factory."

With Kurtz Ersa's rapid growth in the Americas, the new production facility in Chihuahua will better serve local customers, minimize its CO<sub>2</sub> footprint, shorten delivery times and reduce freight

costs, the company said.

The new production plant is expected to commence operations by spring 2024, and will join the company's existing service and logistics hubs in Plymouth, WI, and Guadalajara as its third major service and logistics hub in the region.

### Otis Worldwide Opens PCB Production Center

BERLIN – Otis Worldwide has opened a new €8 million (\$9 million) PCB production facility dedicated to advanced and complex PCB designs, as well as rapid prototyping and industrialization.

With the new production center, located in its SSI1 Electronics Berlin factory, Otis said it is building on the expertise of its Berlin-based teams in the design and production of PCBs, a field of growing strategic importance for many industries.

Otis' PCBs are used in elevators and escalators around the world, and around 75% of the equipment manufactured in Berlin is destined for European construction projects, as well as the modernization market. The remaining 25% is exported overseas.

### SIA Calls for Halt on China Chip Restrictions

WASHINGTON – The Semiconductor Industry Association has called on the US government to refrain from any more restrictions on chip sales to China, saying additional measures against the country could disrupt supply chains and prompt continued retaliation from China.

"Recognizing that strong economic and national security require a strong U.S. semiconductor industry, leaders in Washington took bold and historic action last year to enact the CHIPS and Science Act to strengthen our industry's global competitiveness and de-risk supply chains," the SIA said in a statement released in mid-July. "Allowing the industry to have continued access to the China market, the world's largest commercial market for commodity semiconductors, is important to avoid undermining the positive impact of this effort. Repeated steps, however, to impose overly broad, ambiguous, and at times unilateral restrictions risk diminishing the U.S. semiconductor industry's competitiveness, disrupting supply chains, causing significant market uncertainty, and prompting continued escalatory retaliation by China.

"We call on both governments to ease tensions and seek solutions through dialogue, not further escalation. And we urge the administration to refrain from further restrictions until it engages more extensively with industry and experts to assess the impact of current and potential restrictions to determine whether they are narrow and clearly defined, consistently applied, and fully coordinated with allies."

### Tempo Automation Lays Off Nearly All Employees

SAN FRANCISCO – Tempo Automation in late July laid off 62 of its employees, leaving only seven employees on its payroll in an effort to reduce overhead and keep the company operational, according to an SEC filing.

CEO Joy Weiss and Ralph Richart, Tempo Automation's chief technology and manufacturing officer, are remaining with the company but will cut their base salaries by 50% for the foreseeable future. The company's chief financial officer, Ryan Benton, has resigned.

The company is trying to reduce overhead to better position the company to fund its planned operations while meeting obligations as they come due. Tempo has "experienced negative cash flows since inception that raise substantial doubt about the company's ability to continue," the filing said. The company lost \$7.4 million in the first quarter on revenue of \$2.8 million.

The company said it is working to identify alternative sources of capital and means of reducing expenses that may permit it to continue, including raising debt or equity capital and other alternatives, but there is no guarantee that it will be able to raise additional capital, or that the plan of termination and related workforce reduction will be sufficient to permit the company to continue operations.

Tempo Automation went public in November through a special-purpose acquisition company deal with South Korean firm Ace Convergence Equity Partners that was worth around \$100 million.

Earlier in the month, the firm Tempo Automation executed a \$7 million promissory note with Asia-IO Advanced Manufacturing Partners to finalize the previously announced acquisition of Optimum Design Associates.

#### BRIEFS

### PCD&F

**Aohong Electronics** plans to spend up to 600 million yuan (\$84 million) on a new plant in Thailand that will build PCBs for export.

**DuPont** and **JetCool Technologies** announced a collaboration to increase adoption of advanced liquid cooling technology and introduce a new sales channel that brings JetCool's advanced cooling solutions to semiconductor companies in Taiwan and Singapore.

**Eltek** will receive an additional \$2 million from its insurance carrier to cover costs and damages from a fire at its PCB plant in June 2022. The fabricator has repaid the balance of its \$1.7 million bank debt and is accelerating investments in production equipment.

FTG Circuits Toronto earned qualification for IPC-1791, Qualified Manufacturers Listing.

**Huatong** chairman Jiang Peikun said operations are expected to gradually improve in the latter half of the year, primarily driven by AI and electric vehicles.

**Insulectro** will become exclusive distributor of **Arlon** copper-clad laminates for North America.

**Meiko** will reportedly develop the rigid and flex PCBs required for **Samsung's** Galaxy Ring.

Nan Ya will invest up to 700 million yuan to build a new copper-clad laminate and adhesive sheet production base in Thailand.

Nano Dimension sold a DragonFly IV system to the University of Stuttgart and signed an agreement with a large multinational electronics company to leverage DeepCube's deep learning-based AI technology.

**Renesas Electronics** has standardized on **Altium** 365 PCB design software.

**Rostelecom** launched a new production line of PCBs and telecommunications equipment in St. Petersburg, Russia, as part of its JV with **Russian Telecommunications Technologies.**

**Samsung Electro-Mechanics** is finalizing preparations for the commissioning of its FC-BGA substrate factory in Vietnam.

Siemens Digital Industries Software will expand its collaboration with Amazon Web Services to help IC and electronics design customers leverage AWS's advanced cloud services.

**TSMC** has seen its capacity utilization rates for advanced processes below 7nm rebound slowly since June and is poised to embrace a new wave of chip demand growth in 2024.

**Ventec** announced a cooperative agreement with **Giga Solutions** to offer full workflow solutions to its global PCB and related industry customer base.

**Yijia**, a Taiwanese manufacturer of flexible boards for vehicles, plans to establish a new subsidiary in Vietnam. **#**

### CA

Adco Circuits purchased a Hänel Lean-Lift vertical storage system and Scienscope Reel

Smart incoming material station, installed a new robotic thermal adhesive dispenser, and launched ADCOproto.com – an online tool that provides instant component availability for uploaded BoMs.

Advantest and Arizona State University announced a collaboration with NXP Semiconductors to create a new test engineering course at ASU.

Assembly Solutions purchased two Inovaxe Smart Racks.

Avary Holding implemented Blue Yonder's supply planning solution.

**Benchmark Electronics** celebrated the grand reopening of its facility in Almelo, Netherlands.

**BTU International** signed a strategic partnership with **ANS-answer elektronik** as its reflow oven distributor in Germany.

**Compal Electronics** purchased a \$30 million plot of land in Vietnam to build a new plant and expand production capacity.

Creation Technologies moved into a new 150,000 sq. ft. facility in Changzhou, China.

**Dorigo Systems** chose **CalcuQuote's** QuoteCQ RFQ Management System to upgrade its quote process.

Emerald EMS purchased an Identco ILP-45 label feeder.

**Elista** is investing Rs 350 crore (\$42.7 million) in setting up two electronics goods and appliances manufacturing facilities in Kopparthi, India.

**Foxconn** called off a joint venture with **Stellantis** to design and sell high-end automotive chips. Its Texas-based subsidiary, **S&B Industries**, laid off 115 employees in late July.

Hentec Industries/RPS Automation expanded its distribution agreement with BTU International to include the Vector series of selective soldering systems.

**Heraeus Electronics** announced its participation in the EU-funded research project "ALL2GaN" (affordable smart GaN IC solutions for greener applications).

**Hisense Middle East** signed an MoU with **Condor Electronics** to manufacture and assemble consumer electronics in the Middle East and North Africa region.

**Incap Slovakia** expanded its production area by 1,200 sq. m. due to increasing volumes of customers.

**Jabil** and **Napatech** have collaborated on a server platform for high-bandwidth, lowlatency, financial technology applications.

MacDermid Alpha announced a partnership with Amza for distribution and sales across Israel, Gaza, and the West Bank area.

**NeoTech** installed new automated production and inspection robots to enable a higher level of performance and improve efficiency.

**Orbit International's** Simulator Product Solutions subsidiary received a new contract valued at more than \$2.5 million.

Scanfil expanded its Malmö, Sweden, factory by 2,000 sq. ft.

Seho North America named Lean Stream technical sales representative across northern California and Nevada.

Segue Manufacturing Services expanded its Boston manufacturing facility.

**STP Group** will install a **Hentec Industries/RPS Automation** Pulsar solderability testing system in France.

**Surf-Tech** purchased a **PVA** Delta 8 selective conformal coating machine.

**USI** is expanding its expertise and capabilities in the EV industry by integrating production of powertrain systems.

**Weller Tools** is now offering its Weller Web Communication Platform in EMEA (Europe, Middle East, and Africa) and rest of world.

White Horse Labs purchased a Yxlon Cougar Evo x-ray machine.

**Wistron** will aggressively advance its worldwide manufacturing deployments in response to geopolitical shifts, according to the company's chairman.

venteclaminates.com

### VT-5A2 - Superior thermal performance where size and simplicity matter

**Thermally Conductive Laminate & Prepreg**

With eight times the thermal conductivity of standard FR4, VT-5A2 handles the heat from high-power EPS and motor drives, displays, power circuitry and multi-layer constructions.

#### **Key Features:**

Thermal Conductivity: 2.2 W/mK Tg: 190°C MOT: 150°C T260 >60 minutes

#### **Get in Touch**

EMEA Peter Coakley +44 7976 946 138 peter.coakley@ventec-europe.com

#### Americas

Pesh Patel +1 714 683 7825 pesh.patel@ventec-usa.com

#### Asia

Shawn Peh +65 96 279 906 shawn@ventec.com.cn Germany / DACH Jürgen Knörchen +49 173 421 4625 juergen.knoerchen@ventec-europe.com

### PCD&F

ASC Sunstone Circuits promoted **Kevin Beattie** to production manager and **Matt Stevenson** to vice president and general manager.

**PFOPIF**

Elec & Eltek (Thailand) named Johnny Lye senior manager.

Landis & Gyr named **Russ Pringle** ECAD admin/librarian.

Peters named Britta and Benjamin Alfes to its management team.

### CA

August Electronics appointed Tanya Korenda CEO and Paul Crawford VP of business.

Benchmark Electronics appointed **David Valkanoff** executive vice president and chief operating officer.

Bentec hired Gareth O'Flattery as a technical sales engineer.

Brooks Automation appointed Andrew Balderson senior director, sales & marketing.

Data I/O appointed Gerald Ng vice president of finance.

Deswell Industries announced the passing of chairman Richard P.H. Lau.

East West Manufacturing promoted **Ray Cottrell** to vice president of business development.

Icape Group announced the resignation of CEO **Cyril Calvignac** and the appointment of chief marketing officer **Yann Duigou** as successor.

Incap appointed **David Spehar** managing director of US operations.

Kimball Electronics promoted **Steven Korn** to chief operating officer and appointed **Kathy Thomson** chief commercial officer.

Libra Industries promoted Andrew Williams to president and CEO.

MicroCare appointed Venesia Hurtubise VP of technology & compliance.

RED Semiconductor named **David Harold** head of business development.

STI Electronics hired Tammy Bailey as SMT material handler.

Tompkins Robotics named **Tony Villanova** vice president, PickPal Solutions.

ViTrox appointed Carlos Ponce business development director in Mexico.

# Humidity Controlled Storage

J-STD Storage of PCBs & MSD Components HXD2-1106-01 Our largest heated dry cabinet

.

6

.

#### DRY CABINET STORAGE

XDry humidity-controlled storage cabinets are self-contained, low-maintenance storage systems. There is no need for nitrogen or compressed air, just plug into the wall and they are ready to go! XDry storage cabinets satisfy standards such as IPC/JEDEC J-STD-033 and IPC/JEDEC J-STD-020. The cabinet environment can be maintained from ambient to 1% RH, providing constant & stable storage at precisely desired RH levels.

XDry cabinets are the ideal solution for printed circuit board and moisture-sensitive component storage.

> HXD1-703-02 Small footprint, but high capacity

Corporate Office 3407 County Road 427 Anna, Texas 75409 USA

Phone: 214.296.4868

www.XDry.com

XD1-302-02 Competitively

Priced

sales@XDry.com

0. 0 Mett 11148008

# National News

#### PCB West to Feature Free Expert Advice Sessions

PEACHTREE CITY, GA – Experts in printed circuit design and manufacturing will be on hand at PCB West 2023 to answer attendee questions during the exhibition on Sept. 20, the Printed Circuit Engineering Association announced.

Among the industry experts who will be available are Rick Hartley (signal integrity and noise control), Susy Webb (design layout and routing), Nick Koop (flexible circuits), Stephen Chavez (PCB design), and Keven Coates (design for assembly).

PCB West will take place Sept. 19-22, 2023, at the Santa Clara (CA) Convention Center.

The experts will be available at scheduled times at the PCEA booth during the show hours of 10 a.m. to 6 p.m. Visit pcbwest.com to see the schedule and to register.

"Past attendees have asked for more time to network and get help, and our 'Ask the Experts' series with gurus in signal integrity, high-speed design, EMI, DfM, flex circuits and more is intended to do just that," said Mike Buetow, conference director, PCB West.

The help sessions are free to all expo attendees. Those who register for the exhibition will also have

access to more than 100 leading suppliers to the electronics design and manufacturing industry.

#P

### Booth Sales Open for PCB East 2024

PEACHTREE CITY, GA – The show floor is now open to all exhibitors for next year's PCB East conference and exhibition.

Exhibitors at PCB East 2023 were given a three-week window to reserve for the 2024 event. That exclusive registration ended Jul. 31. Starting Aug. 1, any company may register to exhibit.

The one-day exhibition takes place Jun. 5 at the Boxboro Regency in Boxborough, MA, while the four-day technical conference takes place Jun. 4-7.

"The show floor will be open for three weeks to the 2023 show exhibitors," said Frances Stewart, vice president of marketing and sales, PCEA. "Then we will open it to any companies that want access to the only event for the New England electronics design and manufacturing industry."

In its second year, PCB East 2023 exhibits registration rose 63% from 2022. In all, more than 60 leading suppliers of electronics design tools, manufacturers of bare boards and assemblies, and suppliers of fabrication and assembly equipment and materials exhibited at the show.

Companies interested in exhibiting may visit pcbeast.com or contact Stewart at frances@pcea.net for details.

#### PCEA CURRENT EVENTS BRIEFS

# Chapter News

**Education committee.** PCD&F is undertaking its annual salary survey of printed circuit board designers, design engineers and other layout specialists. Designers for years have taken advantage of the results to benchmark their salaries, benefits and credentials against their peers.

The survey link is https://www.surveymonkey.com/r/2023designersalary.

Results will be published in an upcoming issue. All data collected are revealed only in the aggregate. No individual data are revealed.

Because this is a survey, not a poll, the audience being surveyed is not selected or controlled.

PCD&F has conducted the annual survey of design engineers and printed circuit designers for more than 20 years.

# If you want to be trusted, be reliable.

Your products. A lifespan of reli<mark>ability.</mark>

Fluid Dispensing | Plasma Treatment | Conformal Coating | Selective Soldering **Nordson** ELECTRONICS SOLUTIONS

www.nordson.com/electronics

# Apple Still Sweet for Taiwanese Flex Makers

TAIPEI – The success of Taiwanese PCB flex circuit manufacturers this year will come down to the new iPhone. The Taiwanese Printed Circuit Association (TPCA) says there's a strong correlation between iPhone sales performance and the overall output value of the Taiwan PCB market.

Looking at the third quarter, major flex makers Zhen Ding and Taijun are optimistic about the latest generation of smartphone. Taijun has focused on LCP technology R&D and the development of LCP laminates for high-frequency flexible circuits. The fabricator is also looking at FPC41.11 next-generation technology of Neuro Circuit, which can provide high-speed and low-latency transmission solutions for huge data computing, which will boost AI capabilities.

Industry insiders expect Apple to upgrade its motherboard, which is expected to drive new PCB materials. The market also thinks that the two major features of future iPhones will be the introduction of periscope lenses, which use a prism or mirror to shine light at an angle and enable extremely long zoom ranges, on high-end models, and the migration to USB-C.

| Tuned In<br>Trends in the US electronics equipment market (shipments only) |      |          |                  |     |  |

|----------------------------------------------------------------------------|------|----------|------------------|-----|--|

|                                                                            |      | % CHANGE |                  |     |  |

|                                                                            | MAR. | APR.'    | MAY <sup>p</sup> | YTD |  |

| Computers and electronics products                                         | -0.6 | -0.4     | 0.3              | 3.0 |  |

| Computers                                                                  | -1.6 | 2.4      | 3.9              | 9.4 |  |

| Storage devices                                                                    | 5.6  | 11.1 | 3.6  | 13.3  |  |

|------------------------------------------------------------------------------------|------|------|------|-------|--|

| Other peripheral equipment                                                         | 8.1  | -0.1 | -8.0 | 47.8  |  |

| Nondefense communications equipment                                                | -2.3 | -1.8 | -2.3 | 0.0   |  |

| Defense communications equipment                                                   | -1.0 | 1.5  | 1.0  | 4.7   |  |

| A/V equipment                                                                      | 2.4  | 0.3  | 27.0 | -13.0 |  |

| Components <sup>1</sup>                                                            | -3.3 | -3.1 | 2.1  | 2.2   |  |

| Nondefense search and navigation equipment                                         | 0.1  | 1.4  | 0.4  | 2.3   |  |

| Defense search and navigation equipment                                            | -0.3 | 1.7  | 1.3  | 2.9   |  |

| Electromedical, measurement and control                                            | 1.4  | 0.4  | -0.5 | 1.7   |  |

| 'Revised. PPreliminary. <sup>1</sup> Includes semiconductors. Seasonally adjusted. |      |      |      |       |  |

Source: US Department of Commerce Census Bureau, July 5, 2023

| Key Components                                                                |                                |        |        |        |       |

|-------------------------------------------------------------------------------|--------------------------------|--------|--------|--------|-------|

|                                                                               | FEB.                           | MAR.   | APR.   | MAY    | JUN.  |

| EMS book-to-bill <sup>1,3</sup>                                               | 1.30                           | 1.28   | 1.21   | 1.24   | 1.24  |

| Semiconductors <sup>2,3</sup>                                                 | -20.7%                         | -21.3% | -21.4% | -21.1% | TBA   |

| PCB book-to-bill <sup>1,3</sup>                                               | 0.99                           | 0.91   | 0.88   | 0.89   | 0.98  |

| Component sales sentiment <sup>4</sup>                                        | 82.2%                          | 90.6%  | 88.7%  | 72.2%  | 76.3% |

| Sources: <sup>1</sup> IPC (N. America), <sup>2</sup> SIA, <sup>3</sup> 3-mont | h moving average, <sup>4</sup> | ECIA   |        |        |       |

| 20     |                      |                         |               |                       |         |

|--------|----------------------|-------------------------|---------------|-----------------------|---------|

| 30     |                      |                         |               |                       |         |

| 0      |                      |                         |               |                       |         |

|        | Feb                  | Mar                     | Apr           | May                   | 2016    |

| -      | PMI -                | New briters Product     | invertories - | Customer wyentories - | Backbes |

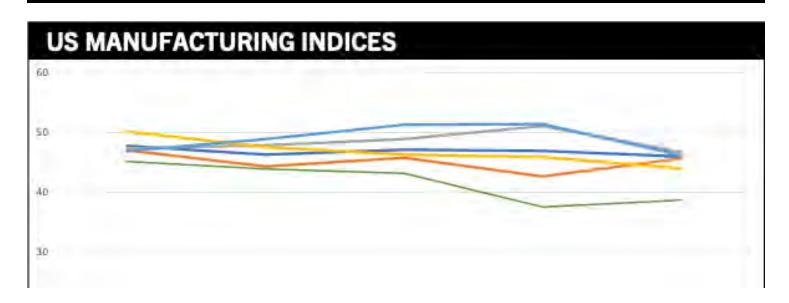

| Source | Institute for Supply | Management, July 3, 202 | 23            |                       |         |

#### Hot Takes

**Printed circuit board and multichip module design software** revenue increased 25.6% to \$368.4 million in the first quarter. The four-quarter moving average, which compares the most recent four quarters to the prior four, rose 15.7%. (ESD Alliance)

Japan's PCB production fell 19.8% year-over-year in April, hitting a two-year low. (JPCA)

Consumers are expected to spend a record \$41.5 billion on **back-to-school shopping** this year, up from \$36.9 billion in 2022 as well as the previous high of \$37.1 billion in 2021. (National Retail Federation)

Worldwide PC shipments totaled 59.7 million units in the second quarter, a 16.6% decrease from the second quarter of 2022, according to preliminary results by Gartner.

North American **EMS shipments** in June rose 0.9% over May and 4.3% from the previous year. Bookings fell 11.5% year-over-year and increased 0.6% sequentially. (IPC)