Morgan: Who Will Own Al-Built Designs?

# <text>

GNIF

Transmission Line Impedance Wirebonding for EV Batteries PCB Thermodynamics This issue of PRINTED CIRCUIT DESIGN & FAB/CIRCUITS ASSEMBLY is brought to you by:

# Instant FULL TURNKEY PCB Quote

PCBTrace provides instant quotes on multiple sets of quantities within minutes.

Visit pcbtrace.com and get a **\$1500** discount.

# Click to learn more

20 YEARS OF MANUFACTURING EXPERIENCE WITH BLIND AND BURIED VIAS, RIGID FLEX & FLEX PCB

# TOP 3 REASONS TO PARTNER WITH IMAGINEERING INC.

# 2 35+ YEARS OF INDUSTRY EXPERTISE AND EXPERIENCE

# **3** FAST TURNAROUND WITHOUT COMPROMISING QUALITY

Some of the biggest brands in the world choose Imagineering for their printed circuit board fabrication and assembly

Whether you're looking for full turnkey services or PCB assembly that uses your parts, our PCB expertise gives you the highest quality printed circuit boards you need and the quick turnaround time you demand.

> Get an online PCB quote in minutes: www.pcbnet.com/quote/

www.pcbnet.com sales@pcbnet.com 847-806-0003 imagineering,inc.

ITAR Registered AS9100D/ISO 9001:2015 SAM Registered RoHS Compliant IPC Member

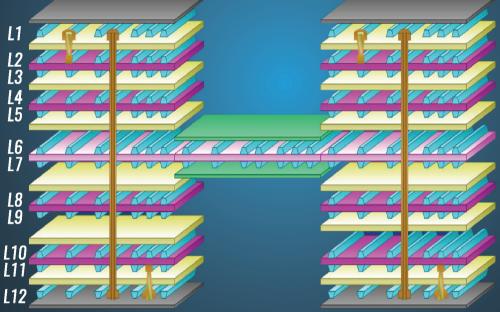

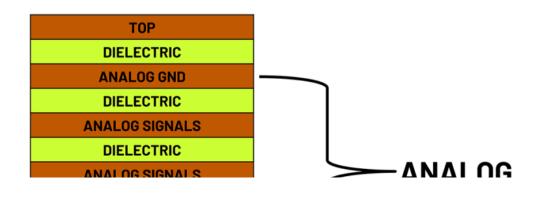

# Multilayer PCB Stackup

12 Layer Flex Rigid, 0.030" Thick Rigid, 0.008" Thick Flex Blind Via L1-L2 & L11-L12, 0.003" Hole, Resin Filled, 0.002"/0.002" Trace/Space, Controlled Impedance

Manufactured on August 2016

# When you're in a rush call RUSH PCB

Affordable Pricing \* Satisfaction Guarantee \* Fast Response \* Free Quote \* Fast Shipping HDI Boards \* Stacked Micro Vias \* 2 mil line & Space \* Flex & Rigid Flex

# Located in the Silicon Valley PCB up to 12 Layers in 3 days PCB Assembly Same Day Turn Full Turnkey Service

Certified: ISO9001/ITAR/UL www.rushpcb.com | Sales@rushpcb.com | 1 408 496 6013 Rush PCB Inc, 2149-20 O'Toole Ave, San Jose, CA 95131, U.S.A

### JANUARY 2024 • VOL. 41 • NO. 1

### FIRST PERSON

THE ROUTE Rules of engagement. Mike Buetow

### MONEY MATTERS

ROI How much securi

How much security is too much? Peter Bigelow

### TECH TALK

**DESIGNER'S NOTEBOOK** Dealing with tricky patterns. John Burkhert Jr.

DESIGN BEST PRACTICES A proactive approach to testing. Stephen Chavez

MATERIAL GAINS Al design brings questions of ownership. Alun Morgan

### ROUGHLY SPEAKING

An exciting new material option. Geoffrey Hazelett

GETTING LEAN Look within for improvements. Anita Tucker

SEEING IS BELIEVING Using leverage against deadbeats. Robert Boguski

### **TECHNICAL ABSTRACTS**

### DEPARTMENTS

**AROUND THE WORLD**

PCEA CURRENT EVENTS

**MARKET WATCH**

**OFF THE SHELF**

## PRINTED CIRCUIT DESIGN & FAB CIRCUITS ASSEMBLY

### **FEATURES**

### **CURRENT TEMPERATURES**

### **Electrical and Thermodynamic Parallels**

Most designers have exposure to the fundamentals of electrical engineering principles, but most have almost no exposure to thermodynamic fundamentals, which can be just as important. A presentation of parallel information on the two disciplines that board designers can use to understand the basic principles of thermodynamics that they often must deal with.

by DOUGLAS BROOKS and DR. JOHANNES ADAM

### SIGNAL INTEGRITY

### How to Calculate Transmission Line Impedance with Dispersion and Roughness, No Field Solver Needed!

Some advanced fast field solvers can provide full S-parameters, but it is also possible to calculate S-parameters using the lossy characteristic impedance and propagation constant. How to compute transmission line impedance using only a Microsoft Excel spreadsheet and no field solver.

by ZACHARIAH PETERSON

### **INDUSTRY TRENDS**

### Nothing Soft about PCB Design Tools Market

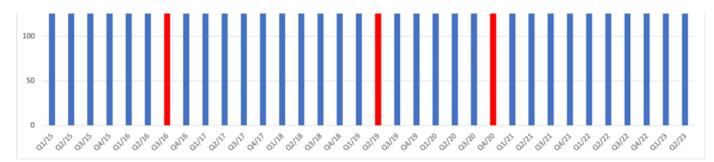

Now up in 21 of the past 24 quarters, sales of PCB design software have more room to grow, according to a host of industry executives.

by MIKE BUETOW

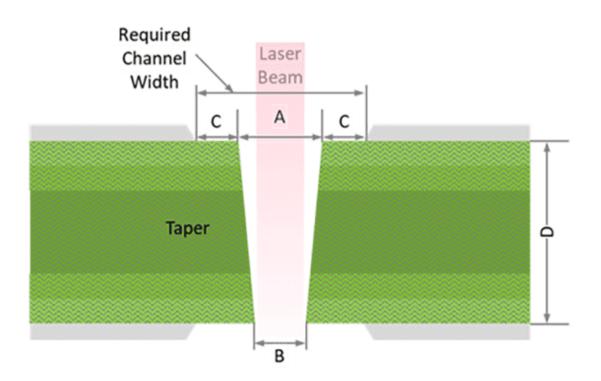

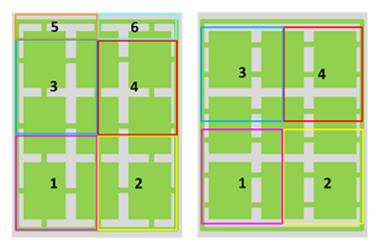

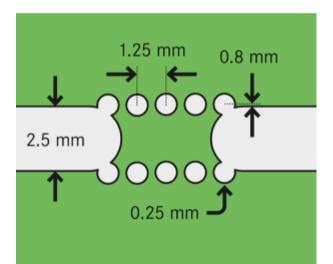

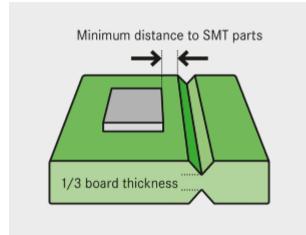

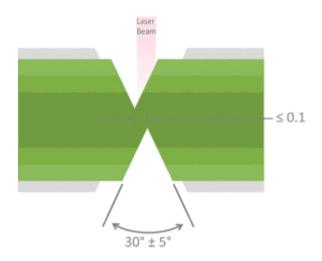

### **DEPANELING** (COVER STORY)

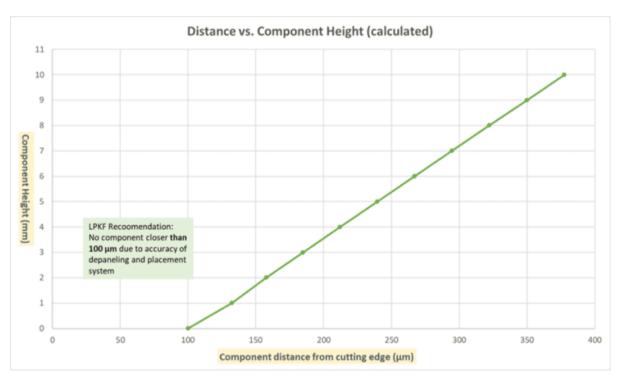

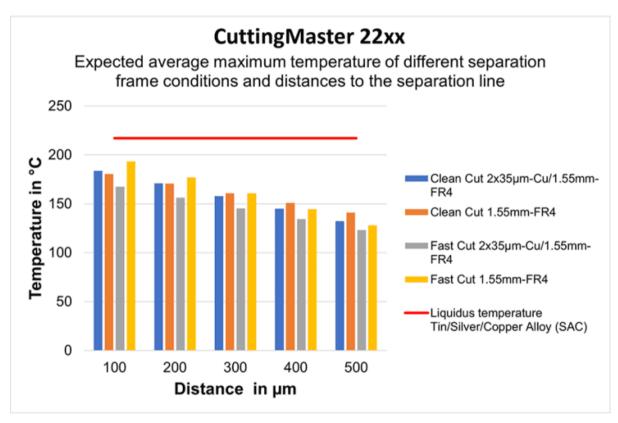

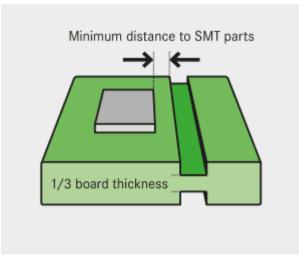

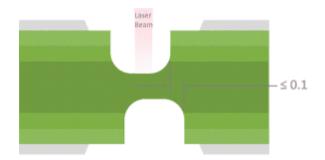

### Establishing Design Rules for Laser Depaneling of Printed Circuit Boards

To exploit the potential of filigree laser tools it is necessary to know and understand the physical and technological possibilities and limitations. A look at the importance of the placement of components close to the cutting channel, as well as factors such as the cutting strategy, arrangement of tabs and the size and positioning of the scan fields to get the best possible performance and quality.

by PATRICK STOCKBRÜGGER and STEPHAN SCHMIDT

### **ULTRASONIC WIREBONDING**

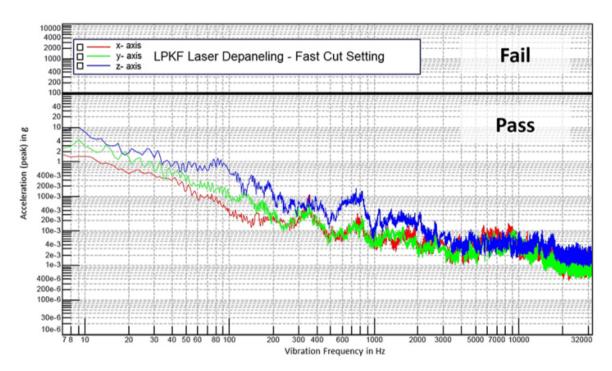

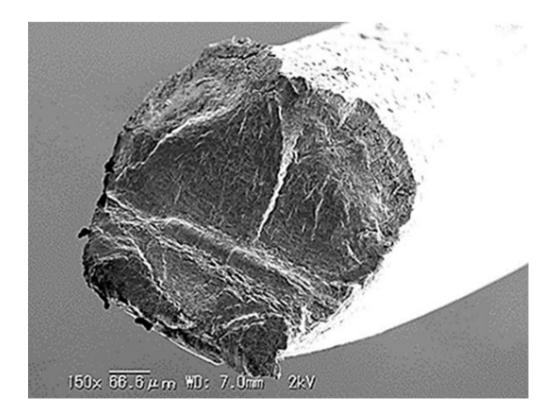

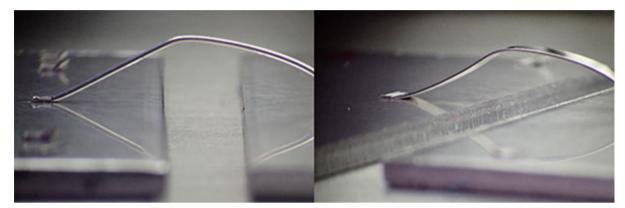

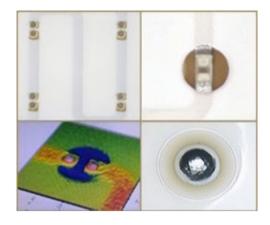

### Vibration Resistance and Durability of Wirebond for EV Batteries

Wirebond technology's flexibility gives it a major advantage as an interconnect method, but its durability is lost in open-air applications. Here, the authors look at ultrasonic wirebonding as currently used in EV battery packs, where they are vulnerable to breakage due to vibration in part because they are not encapsulated. by DODGIE CALPITO, SHUICHI MITOMA, SHIZU MATSUNAGA, KOSUKE ONO and TSUKASA ICHIKAWA

### ON PCB CHAT (PCBCHAT.COM)

**NOVEL WIRELESS / WEARABLE ESD MONITORING**

with DR. DAAN STEVENSON and DR. JONATHAN TAPSON

A Printed Circuit Engineering Association, Inc. publication. All rights reserved.

# Innovation without interruption.

At Chemours, we do more than support high-purity and contamination-free manufacturing processes. As the only U.S. supplier of PFA, an essential material required for semiconductor manufacturing, we're also revitalizing the domestic supply chain.

Because when so much depends on the reliability of microchips, chip makers need a supply chain they can rely on too.

Experience tomorrow, today.

©2024 The Chemours Company. Chemours<sup>\*</sup> and the Chemours logo are trademarks of The Chemours Company.

PCEA PO BOX 807 AMESBURY, MA 01913

### PCEA BOARD OF DIRECTORS

Stephen Chavez, CHAIRMAN Justin Fleming, SECRETARY Gary Ferrari, CHAIRMAN EMERITUS

### MEMBERS

Michael Buetow Tomas Chester Douglas Dixon Richard Hartley Scott McCurdy Anaya Vardya Susy Webb Eriko Yamato

### PCEA.NET

### THE PRINTED CIRCUIT ENGINEERING ASSOCIATION, INC. BRANDS:

| PUBLICATION PCD&F/Circuits Assembly | digital.pcea.net             |

|-------------------------------------|------------------------------|

| WEBSITES<br>PCD&F                   |                              |

| Circuits Assembly NEWSLETTER        | circuitsassembly.com         |

| PCB Update                          | pcbupdate.com                |

| PODCASTS<br>PCB Chat                | pcbchat.com                  |

| EVENTS                              |                              |

| PCB West                            |                              |

| PCB East                            | pcbeast.com                  |

| EDUCATION                           |                              |

| PCB2Day                             | pcb2day.com                  |

| PCEA Training                       |                              |

| Printed Circuit University          | printedcircuituniversity.com |

| AWARDS PROGRAMS                     |                              |

| Service Excellence Awards           | circuitsassembly.com         |

| NPI Awards                          | · · · · ·                    |

|                                     | pcdandf.com                  |

| DATABASE                            |                              |

| Directory of EMS Companies          | circuitsassembly.com         |

### MANAGEMENT

### PRESIDENT

Mike Buetow 617-327-4702 | mike@pcea.net VICE PRESIDENT. SALES & MARKETING

Frances Stewart 770-361-7826 | frances@pcea.net

### PCD&F/CIRCUITS ASSEMBLY EDITORIAL

MANAGING EDITOR

Tyler Hanes 205-258-0067 | tyler@pcea.net

### **COLUMNISTS AND ADVISORS**

Clive Ashmore, Peter Bigelow, Robert Boguski, John D. Borneman, John Burkhert, Jr., Stephen Chavez, Geoffrey Hazelett, Mark Finstad, Nick Koop, Geoffrey Leeds, Alun Morgan, Susan Mucha, Greg Papandrew, Chrys Shea, Jan Vardaman, Gene Weiner

### PRODUCTION

```

ART DIRECTOR & PRODUCTION

blueprint4MARKETING, Inc. | production@pcea.net

Nathan Hoeller | nathan@pcea.net

```

### SALES

VICE PRESIDENT, SALES & MARKETING Frances Stewart 770-361-7826 | frances@pcea.net SENIOR SALES EXECUTIVE Will Bruwer 404-313-1539 | will@pcea.net

### REPRINTS

sales@pcea.net

### **EVENTS/TRADE SHOWS**

EXHIBIT SALES

Frances Stewart 770-361-7826 | frances@pcea.net

TECHNICAL CONFERENCE

Mike Buetow 617-327-4702 | mike@pcea.net

EVENTS MANAGEMENT

Jacqueline Bress 404-955-7675 | jacqueline@pcea.net

### SUBSCRIPTIONS

PRINTED CIRCUIT DESIGN & FAB/CIRCUITS ASSEMBLY is distributed without charge to qualified subscribers. To subscribe, visit pcdandf.com or circuitsassembly. com and click on Subscribe. For changes or cancellations to existing subscriptions: subscriptions@pcea.net

PRINTED CIRCUIT DESIGN & FAB/CIRCUITS ASSEMBLY is published monthly by Printed Circuit Engineering Association, Inc., PO Box 807 Amesbury, MA 01913. ISSN 1939-5442. GST 124513185/ Agreement #1419617.

© 2023, Printed Circuit Engineering Association, Inc. All rights reserved. Reproduction of material appearing in PRINTED CIRCUIT DESIGN & FAB/ CIRCUITS ASSEMBLY is forbidden without written permission.

# OrCAD X

# NEXT GENERATION PCB DESIGN

THIS EVOLUTION OF PC3 DESIGN EXPANDS OUR SERVICES TO CREATE A TOOL THAT IS FASTER, MORE AUTOMATED, AND MORE CONNECTED THAN EVER. DESIGN FAST, CORRECT, CONNECTED.

GET STARTED TODAY >>

**EMA** Design Automation<sup>®</sup>

cadence°

# Shows Remind Us Why People Matter

IT WAS GRATIFYING to see the throngs return for Productronica in November. To the tune of 42,000 visitors, the crowds showed up for the granddaddy of shows in the Western world. (Nepcon Japan is roughly twice as big.)

And there was plenty to see. One of the improvements that jumped out was the increase in speeds, especially on the assembly line. Machine speeds are rising at remarkable rates, with placement machines hitting their fastest speeds ever, even while many of them add multifunctional heads for more flexible line setups.

Yamaha's YRM20 placement machine allows nonstop cart and feeder changes. Fuji's AIMEXR SMT placement machine, for NPI runs, relies on linear motors for its fastest speeds yet. So what if the semiconductor market is predicted to rise by double-digits this year? These machines can take the pressure.

In many cases, the machine is telling the operator what to do, instead of vice versa. Juki's LX-8 SMT platform, for instance, walks users step-by-step through the head exchange process, and then the automatic calibration kicks in.

Innovations that made machines more operator-proof, such as the stencil auto changeover on the Panasonic NPM G/L printer, or in somewhat similar fashion, ITW's Edison II printer, which automates changeovers by first wiping the solder from the stencil and saving it in a reservoir, then automatically loading everything – tooling plate, stencil and blade holders – in the correct orientation from a cart prepped by the operator. Europlacer's new ii-P7 printer is said to have a maintenance-free printhead and cuts cycle times in standard mode by 25%, and by more than 50% with an optional special motor.

BTU's new Aurora convection reflow oven has 16 (!) heating zones, and if that wasn't enough, features dual lanes for high-volume production. Viscom's i56059 AOI performs two-sided inspection for higher speed.

That's just a few of the enhancements from the assembly side. We could go on and on, but you get the idea. Speed is in.

And yeah, there was that crowd which, even spread over four days, felt busy and engaged. All in all, it felt like the trade shows of the past, and in a good way.

Time was, trade shows weren't just for the frontline workers. They were also a place companies would send their benches. They did so for a multitude of reasons: to get their eyes (and in some cases, hands) on the latest technology; to network; and sometimes just to reward them for the work they did (or would have to do).

But most of all, they did so to prepare them to become the next group of lead engineers, Quality Assurance directors, business development directors, and so forth. It was a low-cost way to expose valued staff to the world outside the factory.

Then at some point, they stopped. In some cases, it was economics: Business in North America and Europe fell off its 2001 peaks, and justifying travel became a chore. Many manufacturers reduced their headcounts, leaving their engineering benches a shallow fraction of what they once were. Still others pulled workers in out of fear of losing them to competitors.

While I see evidence that the next generation is joining the industry, in many cases their employers aren't letting them out of the factories. The concern over losing a highly trained worker is real, but in my experience artificially holding them back retards their professional growth and only works for so long. A better strategy is to engage as much as possible with the rest of the industry so that your best employees act as a recruiting and sales tool for your business.

At the PCEA events like PCB West and, coming this spring to the Boston area, PCB East, one of the aspects that stands out is how excited engineers are to be there. And in our post-show

surveys and conversations, they repeatedly bring up the desire to meet others in their chosen disciplines, to the degree that we've been asked to spread out the classes so attendees have more time to pick each other's brains. (We are fiddling with the schedule to accommodate these requests.) We see this firsthand at PCEA, where offering new employees the chance to travel has been a huge plus in talent acquisition.

Remember when perks mattered? I think they still do. And while "perk" to some is synonymous with "expense" and "waste," encouraging and supporting workers who engage in their industry is the kind of perk that keeps valued workers from bolting.

Ingn

mike@pcea.net @mikebuetow

MIKE BUETOW is president of PCEA (pcea.net); mike@pcea.net.

# CAN'T FIND The Right Material?

We offer one-of-a-kind adhesive and encapsulation solutions

www.resinlab.com | 877-259-1669

### NEWS

# SPI, ZDT to Build PCB Plant in Thailand

BANGKOK – SPI has closed a 10 billion baht (\$279.4 million) deal to partner with Zhen Deng Tech to build a PCB manufacturing plant in Thailand.

The investment will establish a plant in Saha Group Industrial Park in Thailand's Prachinburi Province, with a goal to propel Thailand as a key PCB production base in the ASEAN region, SPI said in a release. The company expects an initial investment of 10 billion baht for the first phase and additional investments of more than 50 billion baht (\$1.4 billion) by 2030.

"Saha Group is fully prepared to cooperate with all partners and investors. Our land availability and well-established network in Thailand can help our partner's businesses grow quickly and comprehensively in all aspects," said SPI CEO Vichai Kulsomphob. "Currently, Saha Group Industrial Parks cover four strategic locations across Thailand: 1. Kabin Buri in Prachinburi Province, 2. Si Racha in Chonburi Province, 3. Lamphun in Lamphun Province, and 4. Mae Sot in Tak Province. This investment collaboration with Zhen Ding Tech Group utilizes over 300 rai of land, marking a significant move for the future of Saha Group under the era of technology transformation. This will create over a thousand job opportunities in engineering fields to Thailand. We believe that expanding investment under the concept of Eco-Tech Industrial Park will not only benefit the community directly but also enhance the level of market competitiveness for the overall industry of the country." **C**

# 5G/6G MAESTRO Publishes Materials Development and Electrical Test Roadmap

MORRISVILLE, NC – The International Electronics Manufacturing Initiative (iNEMI) has released the Materials Development and Electrical Test Roadmap, which is part of the 5G/6G mmWave Materials and Electrical Test Technology Roadmap (5G/6G MAESTRO).

MAESTRO, managed by iNEMI, is a joint industry/academia project sponsored by the National Institute of Standards and Technology (NIST) Office of Advance Manufacturing's Advanced Manufacturing Technology (MfgTech) Roadmap Program. This is the second of two roadmap documents that provide a comprehensive 10-year hardware roadmap for mmWave materials development, characterization and electrical test. The first document – Low Loss Dielectric Materials Characterization Roadmap – was published earlier this year.

"This roadmap gives industry an idea of where the technology currently is and where we need to be in the next 10 years to support the development and manufacture of competitive leading edge 5G and 6G networks in the US," says Shekhar Chandrashekhar, CEO of iNEMI.

The substantial information compiled to create the MAESTRO reports and roadmap documents is the result of significant collaboration among individuals in approximately 30 industry and academic settings.

"When teams across the private sector come together around technology roadmapping, their collaborative work creates that optimal R&D plan to achieve real breakthroughs," said Mike Molnar, director of the NIST Office of Advanced Manufacturing. "These technology roadmaps have proved invaluable to advancing US competitiveness and future leadership in building the industries of tomorrow."

This latest chapter of the roadmap focuses on material development needs for several applications and is divided into the following sections: devices (semiconductor technologies), package integration and assembly, antennas and antenna subsystems, thermal management, co-design and multi-physics analysis, and radio frequency (RF) photonics. It also addresses electrical test, identifying gaps, challenges and potential solutions for the electrical testing-related issues of next-generation communication systems.

"It is important for the technical community at 3M and other companies to have access to this kind of roadmap," says Charles Hill, senior research physicist, 3M. "It helps industry identify research and development priorities and know where we can best focus our efforts for our respective businesses."

"Roadmap elements can provide the direction for driving future research and collaboration that are synergistic with emerging applications. The teams contributing to MAESTRO have helped set the stage for creating a pre-competitive environment for 6G systems development," says Professor Madhavan Swaminathan, department head of electrical engineering and the William E. Leonhard endowed chair at Penn State University, and director for the Center for Heterogeneous Integration of Micro Electronic Systems (CHIMES).

**Implementation strategy.** The MAESTRO team was also tasked with developing an implementation strategy to execute the vision of the roadmap and promote the growth of a strong US workforce in RF and mmWave communication technologies. Download a copy of the MAESTRO implementation strategy here.

Several partnerships focused on key findings of the roadmap are currently underway. Examples include:

### Standard Reference Material Development

iNEMI mmWave Permittivity Reference Material Development Project team – developing a permittivity standard reference material (SRM) that will be handed off to NIST in 2024.

Packaging and Integration (including Antenna Subsystems)

- ASIC (American Semiconductor Innovation Coalition) Advanced Packaging team developing a white paper for RF system-in-package (SiP) technical elements to help guide the vision for an advanced packaging manufacturing program.

# Amphenol Acquires Trackwise Designs

STONEHOUSE, UK – Amphenol has acquired Trackwise Designs, a UK-based flex circuit manufacturer that was in financial distress. Terms of the deal weren't initially disclosed.

The new Amphenol Trackwise Designs is a wholly owned subsidiary of Amphenol Sincere, and will support the company's goal to become the leading cell connection system production company in Europe, Amphenol said in a release.

"Trackwise Designs, together with the continuous expansion of the factory in Hungary and the increase of flex printed circuit production capacity in Europe will result in achieving this vision," Amphenol said.

In July, Trackwise announced a delay in the release of its annual financial results after it had failed to secure a contract to supply cell connection system FPCAs to a Tier-1 supplier, and later announced that it was up for sale after its board reviewed future options for the company.

# Dongwei Plans Thai Production Facility

SUZHOU, CHINA – Dongwei Technology, a supplier of vertical plating and surface treatment equipment, has announced plans to build a production base in Thailand, with an investment of RMB61 million (\$8.6 million).

The investment includes the establishment of a new Thai company, purchase of land, construction of factories, purchase and construction of fixed assets and other related matters. The project is located in the Logana Ayutthaya Industrial Park and is subject to approval of the local registration authority.

The company said the investment will help enhance its global sales capabilities, increase penetration in key overseas areas, enhance its global influence and popularity, and strengthen its position in the field of global electroplating equipment.

# UK PCB Supplier Goes Out of Business

WASHINGTON, ENGLAND – Faraday Printed Circuits, a UK-based PCB supplier that operated for more than 35 years, has closed its doors after a drop in orders amid challenging trading conditions.

The company, which was established in 1987 and had expanded from a 4,000 sq. ft. operation to a 22,300 sq. ft. site, fell into administration under FRP Advisory, but the firm was unable to find a buyer for the company.

"Unfortunately, like many other businesses in the manufacturing industry, Faraday Printed Circuits was not immune to a significant fall in demand and mounting external pressures, most notably rising costs, made the business financially unviable," said joint administrator and FRP Restructuring advisory partner Allan Kelly.

The administrators are now preparing to sell the company's assets and have urged interested parties to get in touch. In the company's accounts to the year ending May 31, 2023, its fixed assets were valued at around £737,000 (\$930,000), while liabilities amounted to approximately £1.2 million (\$1.5 million).  $\Leftarrow$

# Icape Acquires German Parts Supplier

FONTENAY-AUX-ROSES, FRANCE – Icape Group has acquired 100% of the assets of Bordan Electronic Consult, a German company specializing in the design of custom-made technical parts.

Since 2002, Bordan Electronic Consult has been developing a range of services focused on the distribution of technical parts to some 30 customers, mainly based in Germany, and offers a wide spectrum of products, of which almost 80% are custom-made. In 2022, the company generated  $\in 0.9$  million in revenue and a gross margin of over 35%.

With the acquisition, Icape has established its CIPEM operation in Germany, dedicated to the distribution of "custom-made" technical parts. The long-term partnerships forged by Bordan will enable the company to diversify its sourcing with suppliers based in Germany, Japan and Taiwan, while also generating potential purchasing, cost and sales synergies in the short and medium term, Icape said in a release.

"We are delighted to be able to integrate Bordan Electronics Consult's assets into Icape Group," said Yann Duigou, CEO, Icape Group. "This well-known German player in the distribution of custom-made technical parts reinforces our position as a technological expert at the service of our industrial customers. This new operation should also generate synergies by pooling our respective know-how. The objective of this acquisition, in line with our external growth strategy and our previous operations in this high-stake territory, will be to participate in the improvement of our local subsidiary's organic growth and profitability."

### ÷P

# Foxconn to Invest \$1.5B in India

TAIPEI – Foxconn will invest more than \$1.5 billion in an Indian construction project to fulfill its "operational needs," the company announced in Taiwanese security filings.

The \$1.54 billion investment was made through a Foxconn subsidiary, Hon Hai Technology India Mega Development, which has been registered in India's Maharashtra state since 2015. A concurrent filing said the same subsidiary would budget the equivalent amount in Indian rupees for a construction project to fulfill "operational needs." The company did not disclose any additional information about the project.

Post-Covid, Foxconn has looked at different strategies for better supply chain resiliency.

Considerations include moving some of its production outside China. Among the pending projects in India are a \$600 million project in Karnataka state and a \$500 million factory in Telangana state. ==

# VDL Acquires Rena Electronica

EINDHOVEN, NETHERLANDS – VDL Groep has announced the acquisition of Rena Electronica, a Dutch manufacturer of smart electronics and LED lighting.

The addition of Rena's specialists and machines will boost VDL's production capacity, particularly with its subsidiary, VDL TBP Electronics, which specializes in printed circuit board assemblies, VDL said in a release.

Rena has a turnover of €12 million (\$15.2 million) and more than 50 employees.

"Our ambition is to be a one-stop-shop industrial partner. Besides our competencies in mechanics and software, with VDL TBP Electronics in our ranks, we've taken a big step forward in electronics," said Willem van der Leegte, president and CEO, VDL. "With Rena's skilled employees and high-quality machines, we're further expanding our production capacity, enabling us to better fulfill the increasing demands of our clients."

"By becoming part of VDL, we'll be able to grow further in added-value innovative solutions together," said Jochem Winkelman, general manager, Rena Electronica. "This acquisition ensures long-term continuity for our clients and employees."

# Hanza Acquires EMS Firm Orbit One

STOCKHOLM – Hanza will acquire all shares in Orbit One, a Swedish contract manufacturer of electronics and electromechanics. Hanza will pay an estimated SEK367 million (\$35.1 million) for Orbit One, plus potential adders based on the company's performance in 2024, up to a maximum of SEK91 million (\$8.7 million). Closing is subject to regulatory approvals, which are expected to be received by early January 2024 at the latest.

Orbit One has annual sales of approximately SEK1.1 billion (\$105 million) with an operating profit (EBITA) of approximately SEK70 million (\$6.7 million). It operates two production facilities in Sweden and one in Poland and has a total of approximately 620 employees, of which approximately 65 are engineers.

Orbit One holds a strong position in the Nordic EMS market and has a stable and diversified customer base, and its acquisition strengthens Hanza's manufacturing cluster in Sweden and Central Europe, adds capacity and expertise in electronics manufacturing and contributes to increased earnings per share, Hanza said in a release.

"Hanza is a good and long-term new owner with the strength and ability to continue developing Orbit One," said Orbit One board member and co-owner Mats Johansson. "We complement each other in an excellent way and the merger creates one of the Nordic region's most competitive contract manufacturers. Furthermore, Hanza, like Orbit One, places great emphasis on creating a good corporate culture with sustainable and sound values. This has been an important factor in the choice of a new owner."

"Orbit One is a respected colleague in the industry that has positioned itself as one of the leading electronics manufacturers," said Hanza CEO Erik Stenfors. "It is therefore with pride that we announce this acquisition that further develops Hanza's manufacturing cluster in Sweden and Central Europe in a very good way. The acquisition is also fully in line with our communicated strategy Hanza 2025."

"Hanza's unique manufacturing concept together with Orbit One's leading position in electronics manufacturing is a perfect combination," added Orbit One CEO Mattias Lindhe. "Together we will be able to develop and expand our businesses and become even stronger in our industry. This deal is good for both our customers and our employees."

# US DoD Awards Nearly \$10M to 7 Microelectronics Firms

WASHINGTON – Seven microelectronics firms received nearly \$10 million in combined funding to commercialize technologies of interest to the US military services as winners of the Defense Business Accelerator (DBX) Microelectronics Challenge. The initiative is funded by the Department of Defense (DoD) and led by the US Partnership for Assured Electronics (USPAE).

The challenge aims to revolutionize how the DoD drives the development of dual-use technology, which can be used for both civilian and military applications. The challenge is testing the hypothesis that the DoD can accelerate growth of a robust domestic industrial base by focusing its resources on commercialization of early-stage, hardware-intensive technologies and then scaling them into resilient businesses in partnership with private capital.

The DBX Microelectronics Challenge offered an opportunity for advanced technology innovators to vie for funding of up to \$2 million each to further commercialize their emerging technologies. The winning companies also will receive commercialization support through an ongoing accelerator program, which includes one-on-one coaching, access to resources and more. The accelerator program's goal is to not only mature the technology but also scale the domestic business to fill critical gaps in the microelectronics supply chain.

After evaluation of 279 submissions received via an open solicitation, 25 finalists pitched their ideas at the Defense TechConnect Innovation Summit on Nov. 28. A panel of industry experts, investors and a DoD representative judged the presentations, selecting the following seven challenge winners for a combined \$9.6 million in funding:

- Freedom Photonics LLC (\$1,500,000)

- Gigantor Technologies (\$2,000,000)

- Momentum Optics (\$1,675,000)

- Mosaic Microsystems (\$1,000,000)

- PseudolithIC, Inc. (\$1,000,000)

- SiliconCore Technology, Inc. (\$1,675,000)

- Soctera, Inc. (\$750,000)

"Typically, the timeline from selection to contract award and receipt of funding is several months. DBX leverages the flexibility of Other Transactions Authority (OTA), along with some innovative structuring of the OTA agreement, to enable awardees to receive funding within 48 hours of their selection at the pitch event," said Christopher Zember, senior fellow for Industrial Base Resilience who is supporting DoD as the architect and lead for this project.

The collaboration between USPAE, a nonprofit organization with members spanning the electronics ecosystem, and the DoD's Manufacturing Capability Expansion & Investment Prioritization Directorate (MCEIP) has been instrumental in driving this initiative forward. Tactical support from Advanced Technology International (ATI), and specifically its TechConnect division, has further fortified the success of the DBX Microelectronics Challenge.

"We're honored to move the area of microelectronics forward with this funding and the ongoing accelerator program that we'll make available to the winners over the next eighteen months," said Nathan Edwards, executive director of USPAE. "The outcome will be faster access to dual-use technologies for which the military services already have a validated interest."

# Commerce Department Announces First CHIPS Act Incentives

WASHINGTON – BAE Systems' New Hampshire-based operations will receive a \$35 million grant to quadruple its production of a chip used in F-15 and F-35 fighter jets in the first CHIPS Act funds to be distributed by the US Department of Commerce.

The award is the first of several expected in the coming months, as the Commerce Department begins distributing the \$39 billion in federal funding that Congress authorized under the 2022 CHIPS and Science Act. The money is intended to incentivize the construction of chip factories in the United States and lure back a key type of manufacturing that has slipped offshore in recent decades. Commerce Secretary Gina Raimondo said that the decision to select a defense contractor for the first award, rather than a commercial semiconductor facility, was meant to emphasize the administration's focus on national security.

"We have been clear since day one that the CHIPS for America Program is about advancing our national security and strengthening domestic supply chains, all while creating good jobs supporting long-term US economic growth," she said in a statement. "As national security becomes as much about the chips inside of our weapons systems as the weapons systems themselves, this first CHIPS announcement shows how central semiconductors are to our national defense."

SEMI and SIA both released statements applauding the first distribution of funding from the CHIPS Act.

The announcement "represents an important milestone on the path to fulfilling the tremendous promise of the CHIPS and Science Act and reinforcing America's national security, critical supply chains, and the economy," said SIA president and CEO John Neuffer. "We applaud Secretary Raimondo and the CHIPS Program Office team for working diligently to begin getting CHIPS incentives out the door. We look forward to additional projects being funded and stand ready to continue working with Commerce Department leaders to ensure the CHIPS and Science Act reinvigorates US semiconductor production and innovation for years to come."

"We commend the thoughtful approach the US Department of Commerce has taken in awarding incentives and are pleased to see the advancement of incentives to bolster the resiliency of the domestic semiconductor supply chain," said Joe Stockunas, president, SEMI Americas. "In order for the global semiconductor industry to support the push for digitalization and a diverse range of smart applications over the coming years, we must go beyond elevating just one facet of the supply chain and pursue a fortified ecosystem encompassing equipment, materials and advanced packaging. SEMI has advocated with the US Chips Program Office to distribute incentives with this goal in mind, and we are confident in their understanding of the industry's needs."

The CHIPS and Science Act provides a 25% tax credit for US facilities that produce semiconductors or chipmaking equipment and \$52 billion in funding for new or updated

semiconductor-related manufacturing programs. The funding includes \$39 billion for grants available to semiconductor manufacturers as well as equipment and materials suppliers and \$11 billion for federal semiconductor research programs. ==

# Ag Express Electronics Establishes Wire Harness Division

DES MOINES, IA – Ag Express Electronics, a provider of solutions, sales, service and support for electronic devices for farmers, agriculture dealers and OEMs, announced the establishment of Integrated Circuit Works, a dedicated division focused on wire harness manufacturing that will expand to include electronics assembly and printed circuit board manufacturing.

The Integrated Circuit Works division, formerly Alliance Group Technologies in Warren, IN, was awarded ISO 9001:2015 by National Quality Assurance (NQA) in August 2023.

"Today, we are focused on wire harness manufacturing and box builds, but in the very near future, the division will expand to feature repair services and printed circuit board manufacturing in an ISO 9001:2015 environment," said COO Eric Randolph.

"Ag Express has always been at the forefront of innovation in the agricultural industry. Our new Integrated Circuit Works division is a natural progression that empowers the company to contribute meaningfully to the success of our clients," added Jim Steinke, chief growth officer. "Achieving this certification reflects the world-class manufacturing culture nurtured at Ag Express and the overall commitment to quality and reliability that runs deep in our company's DNA. As the Integrated Circuit Works division scales, we expect to expand into other industries such as construction, public works, forestry, and more." **GP**

# PCD&F

Chin Poon Industrial will expand its PCB manufacturing capacity in Thailand.

Eltek received five purchase orders totaling \$3.8 million for PCBs.

**Jiangxi Hangde's** 5 billion yuan copper foil project began operation in the Xiaolan (China) Economic Development Zone.

**RS Group** selected **Siemens** as its strategic EDA provider for its DesignSpark Circuit Simulator tool.

Japanese chip materials maker **Resonac** plans to set up a research and development center for advanced semiconductor packaging and materials in Silicon Valley. The former **Showa Denko**, a manufacturer of packaging materials for PCBs, plans to begin operations at its new center in 2025.

Shennan Circuits will build a printed circuit board fabrication facility in Thailand.

**Ventec** expanded its manufacturing capabilities at its Taiwan facility to produce its VT-901/VT-90H polyimide laminates and prepregs. **C**

# CA

**Aegis Software** and **Arch Systems** announced a partnership toward digitizing continuous improvement of factory operations.

Amkor Technology will build a \$2 billion advanced packaging and test facility in

Peoria, AZ.

Altus will distribute Asscon's VP810 vapor phase soldering system.

**Aoxin Semiconductor Technology** is planning a 5 billion yuan IC packaging substrate facility in Huzhou, China.

**Apple** is reportedly allocating product development resources for the iPad to Vietnam.

Astranis Space Technologies purchased a Hentec Industries/RPS Automation Odyssey component lead tinning system.

**Ciena** is expected to begin production of the industry's first pluggable optical line terminals, as well as its optical network units, at a **Flex** factory in the US in mid-2024.

Cursey Technology installed a Europlacer SMT line.

**Cyient DLM** announced the inauguration of a new precision machining facility in Bangalore.

**Delo Industrial Adhesives** has begun its foray into medical electronics applications.

**Dixon Technologies** subsidiary **Padget Electronics** received a manufacturing contract from **Lenovo** to produce laptops and notebooks.

**Element Solutions** placed on Newsweek's list of America's Most Responsible Companies and earned an EcoVadis silver medal for its sustainability efforts.

**Foxconn** was approved to collect \$6.3 million in Wisconsin state tax credits for reaching 1,029 jobs and spending about \$26.7 million on buildings and manufacturing equipment in 2022.

Huawei will move its smart car operations to a new joint company with Changan.

HyRel Technologies named EQC Southeast as its manufacturers' representative.

**India's Ministry of Electronics and Information Technology** is developing a new scheme to bolster electronics component manufacturing within the country.

Inovaxe was named distributor for VisiConsult's x-ray counter solutions in the US.

**Jaltek Systems** and **SG Automotive** signed a collaboration agreement to support demand from the European and UK markets.

**Kasdon Electronics** will supply 180,000 PCB assemblies for the SKA-Low radio telescope to be built in Australia.

PE firm LFM Capital announced an investment in SisTech Manufacturing.

**MAG Capital Partners** acquired a Michigan industrial property in a sale leaseback with EMS firm **MARA Technologies**.

**Offshore Electronics** has invested more than £400,000 into its manufacturing headquarters in St Peter Port, Guernsey.

**OSI Systems** announced new orders totaling approximately \$5 million to provide electronic assemblies to a leading technology OEM.

**Plexus** implemented **Arch Systems'** ArchFX's platform across its SMT lines within its production facilities, and joined the United Nations Global Compact, a voluntary leadership platform for the development, implementation and disclosure of socially responsible business practices.

**Porotech** and **Foxconn** are partnering to advance MicroLED microdisplays for augmented reality applications.

Rocka Solutions appointed PIT Equipment Services as its representative for the

### eastern US.

**Supplyframe** and **Jabil** announced a collaboration to leverage AI and automation for enhanced operations and decision-making in the electronics industry.

SVI Public Co. established a Chinese subsidiary.

**Syrma SGS Technology** has formed a semiconductor-focused subsidiary, Syrma Semico, as well as an electronics and communication-focused subsidiary, Syrma Strategic Electronics.

**Transition Automation** received a large order for advanced holder and blade assemblies from **Rotec BV** in Belgium.

**TRI** announced the expansion of its Malaysian office.

**Variosystems** opened a plant expansion in Sri Lanka, doubling its wire harness and assembly production capacity in the country. **=P**

# Humidity Controlled Storage

J-STD Storage of PCBs & MSD Components

DRY CABINET STORAGE

XDry humidity-controlled storage cabinets are self-contained, low-maintenance storage systems. There is no need for nitrogen or compressed air, just plug into the wall and they are ready to go! XDry storage cabinets satisfy standards such as IPC/JEDEC J-STD-033 and IPC/JEDEC J-STD-020. The cabinet environment can be maintained from ambient to 1% RH, providing constant & stable storage at precisely desired RH levels.

XDry cabinets are the ideal solution for printed circuit board and moisture-sensitive component storage.

> HXD1-703-02 Small footprint, but high capacity

**Corporate Office** 3407 County Road 427 Anna, Texas 75409 USA

Phone: 214.296.4868

www.XDry.com

XD1-302-02 Competitively

Priced

HXD2-1106-01 Our largest heated

.

0

9,

dry cabinet

sales@XDry.com

💿 - 💿 🛛 🖾 🖉 💿 💿 👄

### AROUND THE WORLD

### PEOPLE

# PCDF

Trey Adams

Justin Fleming

Sean Hill

**Cameron Stouder**

Jon Faust

Calumet Electronics appointed Trey Adams vice president and general manager.

Fresh Consulting named Justin Fleming component engineer.

IEC hired **Sean Hill** for sales and service for dry film, chemicals, laminates and phototools.

L3Harris Technologies named **Cameron Stouder** senior specialist PCB design.

Millennium Circuits welcomed John Waite as quality assurance manager.

Sanmina appointed Jon Faust CFO.

### Siemens EDA named Marina Hamdy Zaky customer training engineer. 🚝 P

Xuan Tung Le

**Ramon Hernandez**

Nicolas Denis

Doug Edwards

Charles-Alexandre Albin

David Kalaidjian

Andre Kundert

Brian Kady

Steve Foster

Giuseppe Zanni

Jenny Taymon

Gary Kakos

**Charles Freeman**

AIM appointed Xuan Tung Le technical sales engineer.

ASMPT appointed **Ramon Hernandez** country manager for Mexico.

Asteelflash appointed Nicolas Denis CEO.

Celsia named **Doug Edwards** director of business development.

Escatec appointed Charles-Alexandre Albin CEO, effective Mar. 31, 2024.

Goepel Electronics named **David Kalaidjian** national sales development manager for the US.

Horizon Sales hired Andre Kundert as sales representative for Florida.

Identco named Brian Kady vice president of global sales.

Indium promoted **Steve Foster** to associate director.

Seica Deutschland appointed Giuseppe Zanni branch manager.

STI Electronics added Jenny Taymon to its training team.

Universal Instruments named Curt Anderson general manager, USA and Canada.

Vision Engineering hired Gary Kakos distributor sales executive.

Zentech appointed Charles Freeman GM of Zentech Dallas. 🚝 P

# Measure PCB Surface Finishes ENIG, EPIG, EPAG & ENEPIG

Xray

- XRF with Automated X-Y Table

- Increased Throughput

- Improved Reliability

- IPC 4552 B & IPC 4556

Measuring Made Easy®

www.fischer-technology.com | info@fischer-technology.com | 860.683.0781

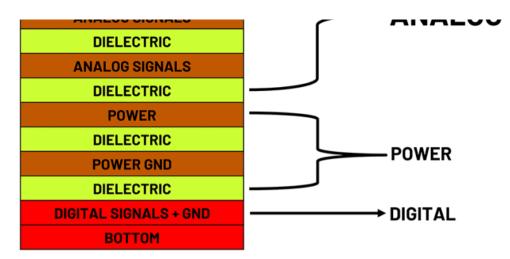

# PCEA Training Announces 2024 PCB Design Classes

PEACHTREE CITY, GA – PCEA Training is offering three five-day training classes next year for printed circuit engineers, layout professionals, and other individuals currently serving in the design engineering industry or seeking to get into it.

Class dates include:

- Class 1: February 5, 12, 20, 26, and March 4

- Class 2: April 5, 12, 19, 26, and May 3

- Class 3: June 14, 17, 21, 24, 28

These instructor-led classes cover the gamut of printed circuit design engineering, from layout, place and route to specifications and materials to manufacturing methods. Schematic capture, signal integrity and EMI/EMC are also part of the comprehensive program.

There are no prerequisite requirements to enroll. Upcoming classes will be held online. All courses are led by experienced instructors.

Registration fees include the 400-page handbook, *Printed Circuit Engineering Professional,* authored by Michael Creeden, Stephen Chavez, Rick Hartley, Susy Webb and Gary Ferrari.

The course includes an optional certification exam recognized by PCEA.

For information about the instructors of the course and authors of the course material, visit pceatraining.net/instructors-authors.

For information about the course overview, class format, and materials to prepare in advance for the class, visit pceatraining.net/course-overview.

To apply, visit pceatraining.net/registration for the next available class or contact Mike Buetow at pceatraining@pcea.net for additional information.

# Al, Containing Heat Focus of Upcoming Technical Webinars

PEACHTREE CITY, GA – Among the member webinars in the coming months are talks on PCB thermal management, the impact of artificial intelligence on electronics, and additive manufacturing.

On Jan. 17, Doug Brooks and Dr. Johannes Adam will present Via and Trace Currents and Temperatures. Rather than thinking of current density, the presenters say, focus on material parameters and properties that determine the temperature of a trace and how these are calculated. Results of some simulations of vias of varying widths and amps will be shown.

On Jan. 23, a panel made up of experts from Siemens, Zuken, CircuitMind and Luminovo, among others, will debate AI in Electronics.

On Feb. 27, Ventec will present on thermal management in materials.

All webinars will include time for audience questions. To register, visit https://pcea.net /events.

PCEA member webinars are free for all PCEA members. Join as an individual member for free at https://pcea.net/pcea-membership. =

# Abstracts Sought for PCB West

**PEACHTREE CITY, GA** – Abstracts are now being accepted for the PCB West 2024 technical conference. The conference, the largest of its kind in Silicon Valley, focuses on training and best practices for printed circuit board design engineers, electronics design engineers, fabricators and assemblers.

The four-day technical conference will take place Oct. 8-11 at the Santa Clara (CA) Convention Center. The event includes a one-day exhibition on Oct. 9.

Papers and presentations of the following durations are sought for the technical conference: one-hour lectures and presentations; two-hour workshops; and half-day (3.5-hour) and full-day seminars.

Preference is given to presentations of two hours in length or more, and no presentations of less than one hour will be considered.

Abstracts of 100-500 words and speaker biographies should be submitted to PCEA. Papers and presentations must be noncommercial in nature and should focus on technology, techniques or methodologies related to printed circuit board design, fabrication, assembly, test, components or packaging, and additive manufacturing.

Submit abstracts at pcbwest.com by Jan. 26. No emailed abstracts will be accepted. Submitters will be notified by early April if their abstract has been accepted. Presentations are due Sept. 6.

Presenters of accepted abstract(s) for the 2024 program receive a complimentary pass to the full technical conference, complimentary access to the online proceedings, and an invitation to the speaker reception.

For more information about PCB West, visit pcbwest.com or contact Conference Director Mike Buetow at 617-327-4702; mike@pcea.net. **EP**

#### PCEA CURRENT EVENTS CH

#### **CHAPTER NEWS**

Portland. The next chapter meeting is scheduled for Jan. 11 at 12 noon and will take place online. The technical presentation is on design rules for laser depaneling of printed circuit boards, presented by Stephan Schmidt. Contact stschmidt@outlook.com for a meeting invitation. Our goal is to continue to have one piece of technical content or discussion at each future meeting to provide more value for all chapter members participating.

#### Support For Flex, Rigid Flex and Embedded Component Designs Now Available.

DownStream's CAM350 and BluePrint-PCB support importation and visualization of PCB designs containing Flex, Rigid Flex or Embedded components. Visualize designs in both 2D and 3D, and easily document complex Flex or Rigid- Flex Stack-Ups for submission to PCB Fabricators.

- Import and Visualize Flex, Rigid-Flex and Embedded Component Designs

- 3D Visualization to Validate PCB Construction and Component Assembly

- Manage Variable Stackup Zones for Rigid-Flex Designs

- Easily Create Custom Flex or Rigid-Flex Fabrication and Assembly Documentation

- Use DFM analysis to analyze a flex or rigid-flex design for potential fabrication or bend related defects

Use Stack Up Visualizer and Blueprint's Rigid-Flex Stackup template to easily manage and document rigid-flex stackups.

A rigid-flex design in 3D. Shown with layers spread to improve visualization of the layer stackup. Use Rigid-Flex and Inter-layer DFM analysis to analyze flex and rigid-flex designs.

For more information visit downstreamtech.com or call (508) 970-0670

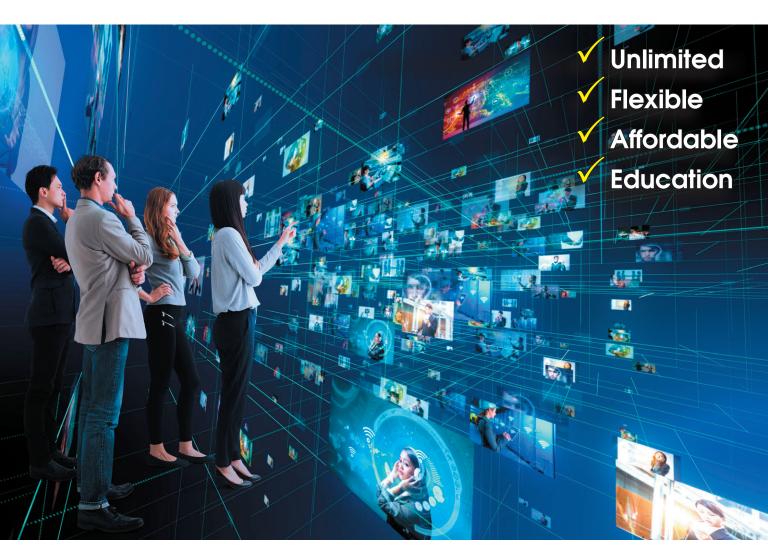

### Reshoring Job Announcements on Record Pace in 2023

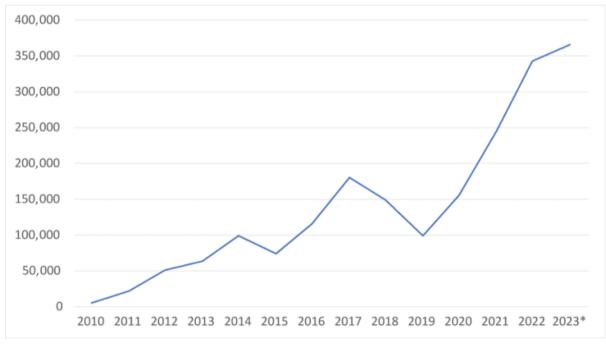

SARASOTA, FL – Reshoring and foreign direct investment job announcements continued their record-breaking run in the first half of 2023, according to the Reshoring Initiative's "1H 2023 Report."

The Initiative expects to see roughly 300,000 jobs announced by year-end, with EV battery and chip investments, along with other essential product industries, accounting for the bulk of the announcements.

Figure 1. Reshoring + FDI job announcements by year, 2010 – 2023 projected.

According to the report, several factors have come to light that substantiate the strength of US reshoring and FDI trends. In the first quarter of this year, average spending on US factory

construction was more than double the average from the past 17 years. Reshoring Initiative data parallels the magnitude and focus of the construction investments.

Independently conducted surveys on reshoring actions by US companies also correlate very closely with Reshoring Initiative data on jobs announced over the past 12 years, adding validity to both data sets.

The "1H 2023 Report" contains data on US reshoring and FDI by companies that have shifted production or sourcing from offshore to the United States.

"We publish this data to show companies that their peers are successfully reshoring and that they should reevaluate their sourcing and siting decisions," said Harry Moser, founder and president of the Reshoring Initiative. "With 5 million manufacturing jobs still offshore, as measured by our \$1.2 trillion/year goods trade deficit, there is potential for much more growth. We also call on the administration and Congress to enact policy changes to make the United States competitive again."

|                                            | % CHANGE |                   |                   |      |  |

|--------------------------------------------|----------|-------------------|-------------------|------|--|

|                                            | AUG.     | SEP. <sup>r</sup> | OCT. <sup>p</sup> | YTD  |  |

| Computers and electronics products         | 0.2      | 0.7               | 0.1               | 1.9  |  |

| Computers                                  | 2.6      | -2.9              | 3.4               | 11.4 |  |

| Storage devices                            | -1.4     | -2.1              | 1.5               | 13.2 |  |

| Other peripheral equipment                 | 9.1      | 3.4               | -3.6              | 26.0 |  |

| Nondefense communications equipment        | -0.5     | 1.5               | -1.1              | -2.0 |  |

| Defense communications equipment           | -3.8     | -1.5              | 4.0               | 3.3  |  |

| A/V equipment                              | -16.2    | -12.7             | -8.4              | 15.6 |  |

| Components <sup>1</sup>                    | 4.8      | 2.8               | -1.2              | 2.3  |  |

| Nondefense search and navigation equipment | -0.9     | 1.2               | -0.2              | 1.4  |  |

| Defense search and navigation equipment    | 0.0      | 0.2               | 0.6               | 3.9  |  |

| Electromedical, measurement and control    | -0.3     | 0.0               | 1.7               | 1.0  |  |

Read the full report here.

Source: US Department of Commerce Census Bureau, Dec. 4, 2023

| Key Components                                                                                                   |        |       |       |       |       |  |  |

|------------------------------------------------------------------------------------------------------------------|--------|-------|-------|-------|-------|--|--|

|                                                                                                                  | JUL.   | AUG.  | SEPT. | OCT.  | NOV   |  |  |

| EMS book-to-bill <sup>1,3</sup>                                                                                  | 1.24   | 1.27  | 1.27  | 1.23  | 1.23  |  |  |

| Semiconductors <sup>2,3</sup>                                                                                    | -11.8% | -6.8% | -4.5% | -0.7% | TBA   |  |  |

| PCB book-to-bill <sup>1,3</sup>                                                                                  | 0.98   | 1.00  | 1.01  | 0.97  | 0.97  |  |  |

| Component sales sentiment <sup>4</sup>                                                                           | 83.0%  | 90.3% | 86.7% | 88.8% | 83.3% |  |  |

| Sources: <sup>1</sup> IPC (N. America), <sup>2</sup> SIA, <sup>3</sup> 3-month moving average, <sup>4</sup> ECIA |        |       |       |       |       |  |  |

#### Hot Takes

**Semiconductor sales** worldwide are expected to contract 9.4% for 2023, followed by a robust recovery in 2024 with an estimated growth of 13.1%. (WSTS)

North American **electronics manufacturing services** in November shipments rose 0.2% from last year and slipped 1.4% from October. Bookings fell 10.1% year-over-year and increased 4.3% sequentially. (IPC)

**India's electronics exports** grew 26% in 2023 to \$26.8 billion, while imports of finished electronic goods dropped to \$13.8 billion in 2023 from \$15.4 billion in 2022. (GTRI)

Global sales of **semiconductor manufacturing equipment** by OEMs are forecast to fall 6.1% to \$100 billion in 2023 but are predicted to rise to a record \$124 billion in 2025. (SEMI)

Worldwide **smartphone shipments** are forecast to see 7.3% year-over-year growth in the fourth quarter. (IDC)

North American **PCB shipments** in November were down 22.5% year-over-year and down 16.3 from October. Bookings fell 9.2% from last year and fell 9% sequentially. (IPC)

Global **semiconductor equipment billings** contracted 11% year-over-year to \$25.6 billion in the third quarter, while quarter-over-quarter billings slipped 1% during the same period. (SEMI)

**Bare PCB imports** into the US soared to 151 million units in October, growing 49% compared with September. (IndexBox)

2024 **semiconductor revenue** will reach \$632.8 billion this year, up 6% from 2023, with the US market remaining resilient from a demand standpoint and China's recovery beginning by the second half. (IDC)

Three-fifths of businesses view **generative artificial intelligence** as a good opportunity but many fear they are exposed to cyberattacks. (PwC)

**AI server shipments** are expected to double in 2024, but while more PCB fabricators are entering the market, they don't expect price competition yet. (DigiTimes)

Global **semiconductor revenue** is projected to grow 16.8% in 2024, to \$624 billion. For 2023, the market declined an estimated 10.9% to \$534 billion. (Gartner)

The **PCB market** will grow 4.9% year-over-year in 2024, driven by gradual improvement in demand for consumer products such as mobile phones, PCs and notebooks, plus new applications such as electric vehicles, AI servers and satellite communications. (Prismark Partners) Revenues among the **40 leading PCB suppliers,** which account for over one-half of industry sales, fell year-over-year but grew sequentially in Q3. Year-to-date aggregate revenues were down through September. (Prismark Partners)

# SAVE THE DATE!

Conference & Exhibition Engineering *Tomorrow*'s Electronics

PCB WEST 2024

**CONFERENCE:** October 8 – 11

**EXHIBITION:** Wednesday, October 9

Santa Clara Convention Center, CA

#### PCBWEST.COM

#### **Bureaucracy Blues**

#### Over-the-top security controls can do more harm than good.

IS THE BUREAUCRACY of security making us all less secure? That is a question I find myself asking increasingly as layer after layer of bureaucracy in the form of forms, protocols and additional steps makes quoting, receiving orders, building product and then shipping and invoicing more cumbersome and time-consuming.

Don't get me wrong: I believe in quality and security, especially in the world we are living in and with the cyber-reliant environment we must utilize to communicate and share data among people and businesses. Increasingly, however, some measures that are intended to increase security instead have the effect of wasting time, adding cost and extending lead times to deliver much-needed product.

To wit: A customer requested a quotation for a few spare parts from a previous production run. To obtain the quote required logging on a "secure" website to download the RFQ and then uploading the completed quotation through the same web portal. The customer then sent an email notification that there was an order, again logging on the website to download the purchase order. In this case, the customer's quality clauses required both a new FAI and Source inspection. To comply, it required logging on the same web portal – twice. After Source took place, it required two more times of logging on the website to download documentation to ship. After shipping, once again it was necessary to log on the site to invoice. I added up the number of hours required to do the extra steps for this order and found it took longer to "process" the quotation, order and shipment than it did to produce the product in the first place! Had this part been technology-rich I might understand; however, this order was for pieces of shim stock! It has not always been this way. A great example is the development of the P-51 Mustang. For younger readers, this was not a Ford automobile but a fighter aircraft, considered among the greatest fighter planes of its era. Back in World War II, a time where the need for security was as important as it is today, a team came together and in 30 days designed the P-51. A purchase order was placed, and 102 days later, the prototype was tested. After 44 more days, the plane was coming off production lines and successfully in service. That is 176 days from concept to being in service! How could it happen so fast? Clearly, with a war on, there was a pressing need, combined with a heightened sense of urgency by all. I suspect, however, there was also much less unnecessary paperwork and bureaucratic documentation. Time spent on anything unnecessary meant added time or delays in accomplishing the more important tasks.

Fighter planes of today are far more complex than those of 80 years ago, but my guess is that today the fastest a plane could go from concept to being successfully in service would be closer to 176 months, if even that fast. It should not take as long as it now does for more basic items to go through the quote/procurement/manufacture/ship/invoice processes, however. There is a real opportunity for improvement for companies to streamline the security and quality bureaucracy to be globally competitive technologically – and more importantly – in time to market.

More importantly, it is applying the appropriate inspection and security needed for different types of products, technologies and end-uses. One size does not fit all, and more is not always better. Some may want to simplify security protocols by making all components, all parts and all items for an end-product require the same levels of security. It appears a healthy dose of common sense is needed in many situations to simplify the basic and expedite the ability to respond and deliver.

Going back to my first example, is it necessary or does it provide any real value to require a Source inspector to go on site to inspect a shim? Or is the product it is going into more secure because such a basic part being inspected onsite. I later learned that this company made a blanket decision that all components of all types that go into a particular program require Source inspection. This one-size-fits-all decision will most likely cost critical time-to-market for the product and undoubtedly add significant and unnecessary cost to the end-product. As technology advances, products become more complex all while the competitive tensions throughout the world heighten, so the need to be cognizant of preserving security and assuring quality is necessary. All should equally strive to be prudent when applying security protocols and inspection processes, however. Consider the part, component or processes' actual potential for security risk and then apply the appropriate level to the situation. Again, consider how much quality documentation is appropriate for each specific item. Clearly highly sensitive circuitry requires far more thorough quality review and levels of inspection, as well as greater security protocols, than a shim, washer or screw.

The goal should be to quickly develop and deliver high-quality product while doing so with the appropriate level of security. By investing some time to determine the appropriate levels of security differentiate the needed quality requirements will save time and money for all companies, departments and people involved.

**PETER BIGELOW** is president of FTG Circuits Haverhill; (imipcb.com); pbigelow@imipcb.com. His column appears monthly.

# PCB EAST 2024 Conference & Exhibition

Engineering Tomorrow's Electronics CONFERENCE: June 4 - 7 EXHIBITION: Wednesday, June 5

Boxboro Regency Hotel & Conference Center, MA

WHO'S EXHIBITING

**Accurate Circuit Engineering All Flex Solutions Allfavor Technology** Altair APCT Archer Circuits Company, Ltd. **Cadence Design Systems DownStream Technologies Electronic Interconnect EMA Design Automation Fine-Line Circuits Limited.** Fischer Technology Inc. Freedom CAD Services, Inc. **GS Swiss PCB** Identco Imagineering, Inc. InfraTec infrared LLC InstaDeep LTD

**Newgrange Design PalPilot International Corp PCB Technologies USA Polar Instruments, Inc. Printed Circuit Board Association of American (PCBAA) Printed Circuit Engineering Association (PCEA)** Quantic Ohmega / Ticer Technologies LLC RBB **Screaming Circuits** Sourceability Starteam Global Surface Mount Technology Association (SMTA) **Sunstone Circuits** SVTronics, Inc. **Trilogy-Net Inc. Trylene Inc. Ventec International Group XDry Corporation**

#### **PCBEAST.COM**

## Printing Analog Circuit Elements Directly on the PCB

Prepare yourself for unusual circuit patterns.

THERE IS NO free lunch when it comes to populating a printed circuit board. Every part has a cost and a failure rate. One of the first projects of my career was a pulse-Doppler surveillance radar called PSTAR. In typical military jargon, that acronym stands for "Portable Search and Target Acquisition Radar."

My part was the amplifier module that was subdivided into various blocks for easy field service. One of the sub-blocks was a 20dB coupler. It lived inside its own hermetically sealed aluminum housing. The PCB inside had two traces that ran alongside each other, giving the circuit four ports with feedthroughs to the outside world. SMA connectors and semi-rigid cables wired the various modules together.

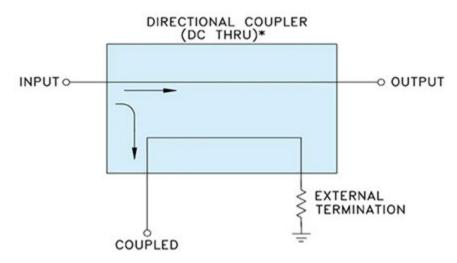

Figure 1. The typical broadside coupler will have the ports organized as shown while a quadrature hybrid coupler will flip the

# output and termination port, which requires two layers on the PCB. (Source: Mini-Circuits)

My responsibilities included the little housing for the coupler, the overall mechanical packaging and all the semi-rigid cable drawings, as well as the RF amplifier. The control board was the only part designed by an external vendor. Meanwhile, the PCB for the coupler had no more than a single  $50\Omega$  termination resistor and the feedthrough connectors. We did not yet have PCB design software at that company, so this was done with AutoCAD.

That was back in 1990, but I still remember that simple board that was little more than a mirrored shape. At its core, the coupler is represented by the two transmission lines running parallel for a distance equal to a quarter of one wavelength of the resonant frequency, which was 13cm; somewhere in the 900MHz range. That type is known as a directional coupler.

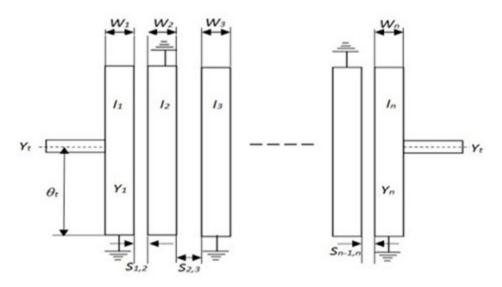

Figure 2. The interdigital bandpass filter bears a strong resemblance to this diagram. (Source: International Journal of Scientific & Engineering Research)

Quadrature hybrid couplers. Another type, a quadrature hybrid coupler, can also be printed, although the transmission lines are created on adjacent layers. The trick here is that layer-to-layer registration becomes important, particularly as the lines get thinner. Due to stackup realities, the  $50\Omega$  stripline may be something like  $100\mu$ m. Now, if the layer-to-layer misregistration is  $25\mu$ m off in the direction that affects the two lines going belly-to-belly, then the coupling will drop off 25%.

Facing this exact problem, I went to the PCB West conference carrying a rolled-up blueprint with fab notes regarding the layer-to-layer constraint among other challenges. This was rather unexpected among the PCB fabrication vendors on the exhibition floor, but they would all stop what they were doing when I unrolled that D-size print. Most of the vendors had to pass on the chance to do this job but a few would take on the precise registration spec by imaging both sides of the core simultaneously.

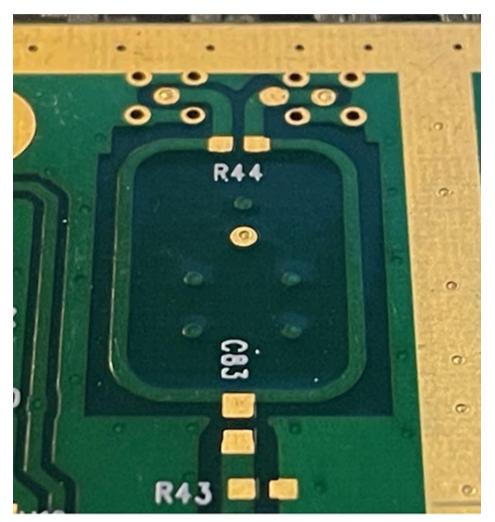

Figure 3. A Wilkinson divider circuit as part of a feed-forward correction board that controls the amplifier at the base of a cellular tower. In many cases, the solder mask is opened, leaving only a thin dam to contain solder on the SMD pads. (Source: Author)

**Interdigital filters.** Another type of component that can be etched rather than placed on the board is the interdigital filter. This circuit element owes something to the broadside coupler

element. Microwave signals propagate across fairly wide gaps, making this a more manufacturable item, which would be printed on the outer layers. The stub length is again determined by the 1/4 wavelength. The rest is a complex mathematical formula.

Wilkinson combiners/dividers. When you want to combine or divide RF transmission lines without inducing a phase shift, the Wilkinson element comes in handy. To be fair, this does require a balance resistor at the business end. As you may have guessed, the length of the lines is determined by the resonant frequency (wavelength) of the radio. We're looking at about 3cm on each branch in this case.

**Finally, a printed inductor.** This one was a bit tricky since the trace goes from a signal net directly to ground. The squared off spiral inductor in **Figure 4** extends from the transmission line and ends with a via to ground. Of course, it is also surrounded by ground pour that we don't want shorting to the signal path. A route keep-out around the edges provides that assurance.

Figure 4. The same PCB as in Figure 3, and noted for being the first layout I did using Cadence Allegro. The 1997 date code puts this in the early 3G CDMA era. (Source: Author)

It seems that analog boards lend themselves to unusual circuit patterns. Matching networks can include tuning stubs that can be cut or extended with little copper tabs. Stray noise can be isolated with a band of grounded copper. Thermal dissipation can be enhanced with a tightly spaced grid of vias on an exposed copper plane. Replacing resistors, filters and heatsinks may take some PCB real estate, but earns it back by reducing the BoM cost, along with the potential for mitigating assembly defects.

JOHN BURKHERT JR. is a career PCB designer experienced in military, telecom, consumer hardware and, lately, the automotive industry. Originally, he was an RF specialist but is compelled to flip the bit now and then to fill the need for high-speed digital design. He enjoys playing bass and racing bikes when he's not writing about or performing PCB layout. His column is produced by Cadence Design Systems and runs monthly.

#### Analysis on the Move

Shifting critical processes "left" is a more proactive approach to testing and validation.

PRINTED CIRCUIT BOARD (PCB) design is a critical aspect of electronics product development, influencing the overall functionality, reliability and performance of electronic devices. Understanding the significance of analysis in PCB design and emphasizing its role in ensuring the integrity of electronic systems is key to success. The rapid evolution of electronic devices demands increasingly sophisticated PCB designs. As electronic components become more compact and complex, the need for thorough analysis in the design phase becomes paramount.

Analysis in PCB design involves evaluating various factors such as signal integrity, thermal performance, power distribution, and electromagnetic interference to guarantee the functionality and reliability of electronic systems. Implementing analysis early in the design cycle contributes to the optimization of PCB layouts, signal integrity and electromagnetic compatibility (EMC), thermal management, power distribution and overall functionality.

Surprisingly, many teams still choose to skip the analysis step entirely in an attempt to reduce project schedules and cost. This often causes costly project delays and increased cost downstream due to issues that could have been addressed if an analysis had simply not been skipped.

The ever-evolving landscape of electronics systems design demands a true paradigm shift in the approach to analysis, and that is "shifting left." We'll explore the principles, methodologies and advantages of shifting left analysis in PCB design, aiming to accelerate innovation and enhance the reliability of electronic systems.

Traditionally, the PCB design process followed a sequential approach, with testing and validation occurring towards the later stages of the flow. Shifting left analysis proposes a proactive strategy by moving testing and validation processes earlier in the design cycle, enabling rapid identification and resolution of potential issues before it's too late.

Principles of shifting left analysis:

- Early integration of analysis tools. Integration of simulation tools at the early stages of design enables engineers to assess the performance and reliability of the PCB. Analyzing signal integrity, power distribution and thermal considerations early on helps in making informed design decisions and preventing respins.

- **Collaborative design environment.** Collaboration between different design disciplines (electrical, mechanical and software) is crucial for a successful shifting left strategy. Early engagement of cross-disciplinary teams facilitates quick identification and resolution of design conflicts.

- Automated design verification. Leveraging automated design verification tools ensures that design rules and constraints are checked continuously throughout the design process. This reduces the likelihood of errors and accelerates the identification

of potential issues.

Methodologies in shifting left analysis:

- **Design for reliability (DfR).** Incorporating DfR principles early in the design process ensures that reliability is built into the product from the outset. Analysis of failure modes and stress factors aids in the development of robust and reliable PCBs.

- Virtual prototyping. Utilizing virtual prototypes (the digital twin) enables designers to assess the behavior of the PCB in a simulated environment. This allows early detection of design flaws and optimization for performance and reliability.

- **Continuous testing and validation.** Implementing continuous testing and validation processes ensures that the design is rigorously evaluated at every stage. Early identification of issues minimizes the likelihood of costly design changes later in the development cycle.

Advantages of shifting left analysis:

- **Faster time to market.** By addressing potential issues early in the design process, the overall time to market is significantly reduced.

- **Cost reduction.** Minimizes need for costly redesigns and reiterations, leading to cost savings in the product development cycle.

- **Enhanced product reliability.** Early identification and resolution of design issues contribute to the development of more reliable and robust PCBs.

- Improved collaboration. Cross-disciplinary collaboration is enhanced, fostering a more integrated approach to product development.

The importance of analysis in PCB design cannot be overstated. Thorough analysis is a proactive approach to identifying and addressing potential issues before they manifest in the final product. Signal integrity analysis, schematic analysis, thermal analysis, power distribution analysis, EMC analysis and manufacturability analysis collectively contribute to the optimization of PCB layouts, ensuring reliable and high-performance electronic systems.

Shifting left analysis is a transformative approach to PCB design that offers substantial benefits in terms of speed, cost and reliability. Embracing this methodology enables designers to proactively address potential issues early in the development cycle, ultimately leading to more innovative and reliable electronic products.

As technology continues to advance, the role of analysis in PCB design will only become more critical in meeting the growing demands for smaller, faster and more reliable electronic devices. The adoption of shifting left analysis in PCB design is poised to become a cornerstone of success in the electronics industry.

STEPHEN CHAVEZ is a senior printed circuit engineer with three decades' experience. In his current role as a senior product marketing manager with Siemens EDA, his focus is on developing methodologies that assist customers in adopting a strategy for resilience and integrating the design-to-source Intelligence insights from Supplyframe into design for resilience. He is an IPC Certified Master Instructor Trainer (MIT) for PCB design, IPC CID+, and a Certified Printed Circuit Designer (CPCD). He is chairman of the Printed Circuit Engineering Association (PCEA); stephen.chavez@siemens.com.

# Why Become a **PCEA Corporate Member?**

- Information, opportunities & marketing channels to

highlight your brands,

products & services

to buyers & users worldwide

- Inclusion in the PCEA Member Directory, a product & service guide for buyers & users

- Free advertising of your products & services to more than 50,000 design engineers, fabricators & assemblers

- Discounts on trade shows, technical conferences, online learning platforms & webinars

# Join today: pcea.net/pcea-membership

Offering price points to meet every company's budget and needs!

## Who Will Own Al-Built Designs?

Generative AI could transform product design, but raises questions about creative ownership.

THE RECENT OUSTING and subsequent rehabilitation of OpenAI's CEO added some theater to the debate and buzz around artificial intelligence. AI, it seems, is everywhere and in everything from our smartwatches and phones to automobiles, data centers and factories.

With the explosion in generative AI like OpenAI's ChatGPT, it's also taking on creative roles that we might have assumed would remain the preserve of human intellect. For a while now, it has been possible to generate realistic images of human faces – not copies but unique individuals that never existed except inside a computer. Also, in 2023, the fashion brand Levi's became one of the first companies to suggest it would use AI-generated clothing models. These are expected to improve the shopping experience for customers by helping them assess clothes on likenesses that have a similar body shape and size to their own. Of course, it's also likely to help brands cut marketing and merchandising costs.