Burkhert: What is Wafer-Level Chip-Scale Packaging?

pcdandf.com circuitsassembly.com February 2024

#### PRINTED CIRCUIT DESIGN & FAB USION 2024 CIRCUIT DESIGN & FAB CIRCUIT SIGN CONTROL CONO

Understanding the Sources of Crosstalk

## Mixed Signals

- Effects of Trace Coatings and Via Fillings

- Touring Chicago's Assembly Shops

- EMA's CAD Spinoff

- A Closer Look at HDI

### Flex PCB Assembly & Manufacturing

Get your Custom PCBs exceptionally fast and perfectly tailored to your business needs with our complete dedication to quality and high performance.

### Click to learn more

20 YEARS OF MANUFACTURING EXPERIENCE WITH BLIND AND BURIED VIAS, RIGID FLEX & FLEX PCB

# Making artificial intelligence smarter.

As technology becomes more integrated with daily life, we're making semiconductor technology more reliable.

From preserving the highest levels of system purity to protecting critical process tools, our solutions deliver the performance semiconductor manufacturers need to power a smarter, safer, more connected future.

www.chemours.com/semiconductor

Experience tomorrow, today.

©2024 The Chemours Company. Chemours" and the Chemours logo are trademarks of The Chemours Company.

RUSHPCB

20 YEARS OF MANUFACTURING EXPERIENCE WITH BLIND AND BURIED VIAS, RIGID FLEX & FLEX PCB ELECTRONIC DESIGN, & QUICK TURN CIRCUIT BOARDS, ASSEMBLY & FULL TURNKEY

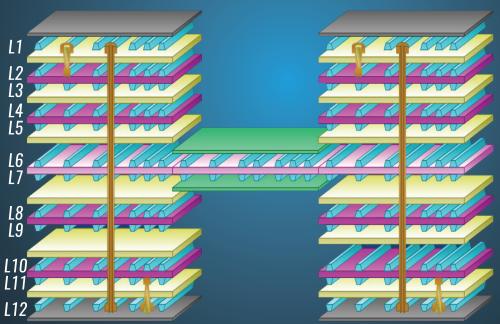

### **Multilayer PCB Stackup** 12 Layer Flex Rigid, 0.030" Thick Rigid, 0.008" Thick Flex Blind Via L1-L2 & L11-L12, 0.003" Hole, Resin Filled,

0.002"/0.002" Trace/Space, Controlled Impedance

Manufactured on August 2016

### When you're in a rush call RUSH PCB

Affordable Pricing \* Satisfaction Guarantee \* Fast Response \* Free Quote \* Fast Shipping HDI Boards \* Stacked Micro Vias \* 2 mil line & Space \* Flex & Rigid Flex

### Located in the Silicon Valley PCB up to 12 Layers in 3 days PCB Assembly Same Day Turn Full Turnkey Service

**Certified: ISO9001/ITAR/UL** www.rushpcb.com | Sales@rushpcb.com | 1 408 496 6013 Rush PCB Inc, 2149-20 O'Toole Ave, San Jose, CA 95131, U.S.A

#### FEBRUARY 2024 • VOL. 41 • NO. 2

#### FIRST PERSON

THE ROUTE Message for the future. **Mike Buetow**

#### MONEY MATTERS

#### ROI

Finding a middle ground. **Peter Bigelow**

**BOARD BUYING** New year, new cost savings. **Greg Papandrew**

#### **FOCUS ON BUSINESS**

Tailor business to your customers. Susan Mucha

#### TECH TALK

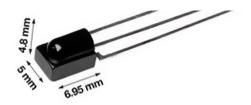

**DESIGNER'S NOTEBOOK** Get to know WLCSP. John Burkhert Jr.

#### **DESIGN BEST PRACTICES**

More power through multiple boards. **Stephen Chavez**

#### **MATERIAL GAINS** The PCB space race.

Alun Morgan

#### **ROUGHLY SPEAKING**

New skills on the block. **Geoffrey Hazelett**

#### THE FLEXERTS

Eliminating through-holes. Nick Koop

#### **TECHNICAL ABSTRACTS**

#### DEPARTMENTS

#### **AROUND THE WORLD**

PCEA CURRENT EVENTS

**MARKET WATCH**

**OFF THE SHELF**

# PRINTED CIRCUIT DESIGN & FAB

#### **FEATURES**

#### CONDUCTIVITY

#### Do Trace Coatings or Via Fillings Improve (Thermal or Electrical) Conductivity?

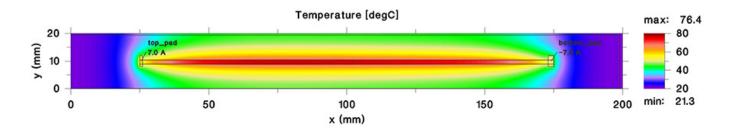

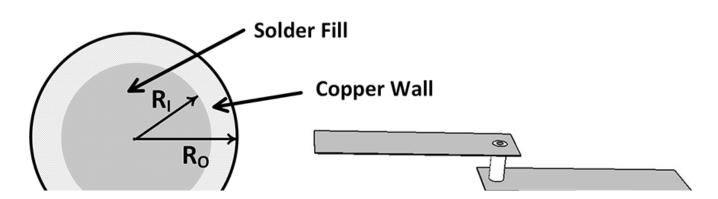

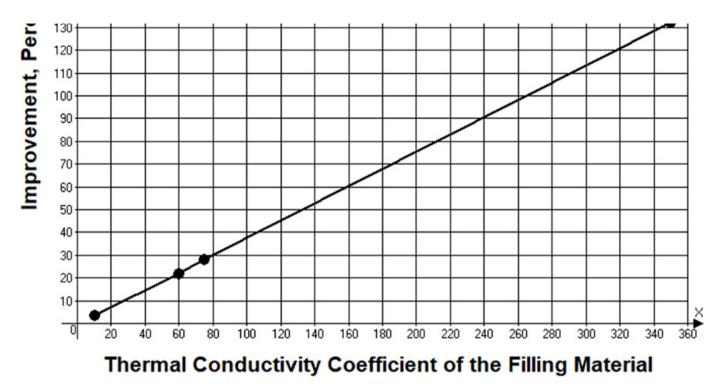

A number of people and board manufacturers suggest that coating a trace or filling a via cavity can result in significant thermal and/or electrical conductivity improvements, but this is usually not the case. A look at via fillings and trace coatings and the effect that different materials can have on conductivity.

by DOUGLAS BROOKS and DR. JOHANNES ADAM

#### SIGNAL MODELING (COVER STORY)

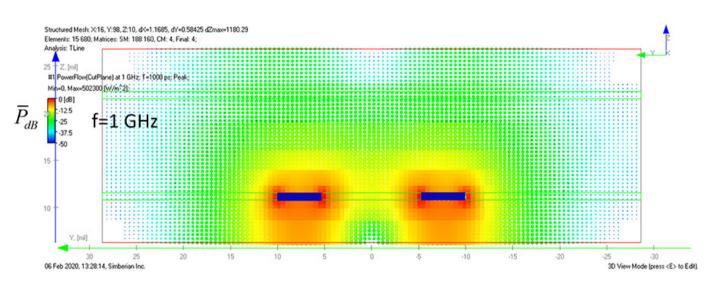

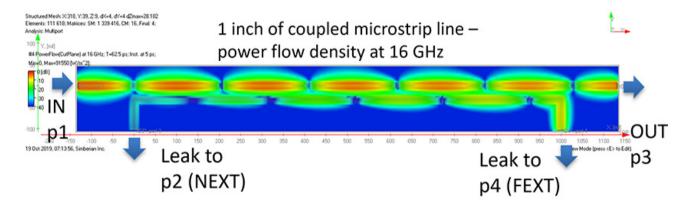

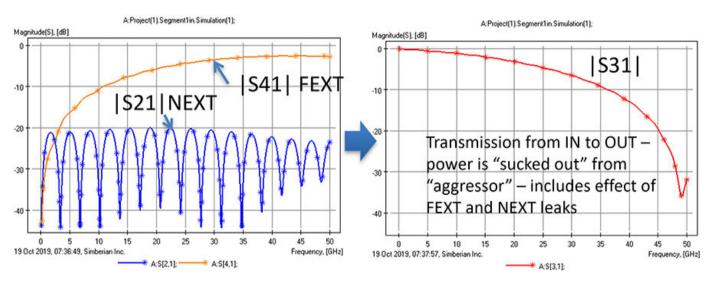

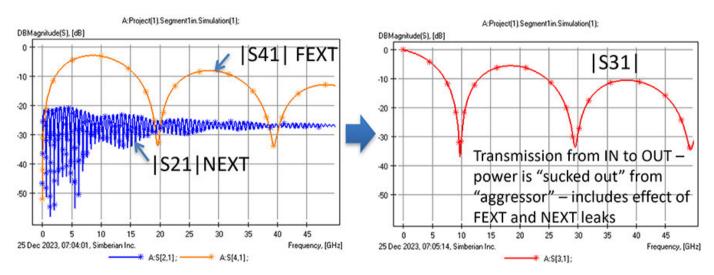

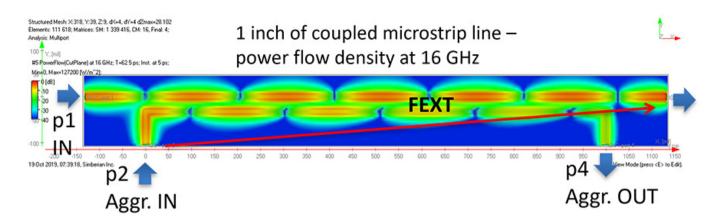

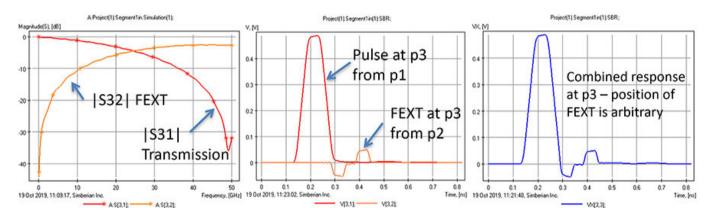

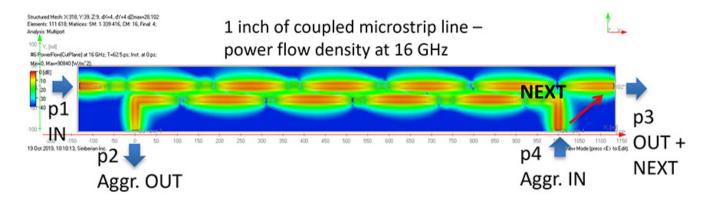

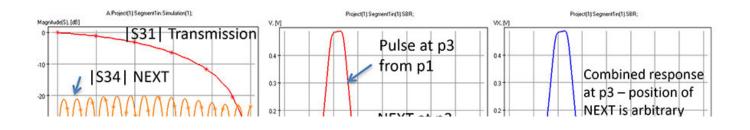

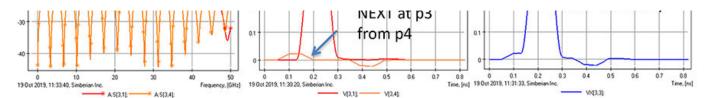

#### How Interconnects Work: Anatomy of Crosstalk

Crosstalk in PCB and packaging interconnects can cause signal degradation that results in costly redesigns, but many designers do not know how to correctly identify its sources and mitigate its effects. An overview of crosstalk sources and terminology, plus models for identifying its effects.

by YURIY SHLEPNEV. PH.D.

#### LEFT SHIFT

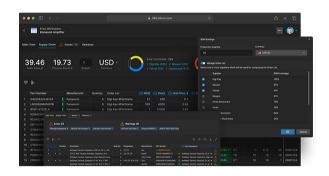

#### **Building the Efficient Design System**

EMA Design Automation recently announced that it will be spinning off its software products for library management, component supply chain data, and other areas into a new company. Accelerated Designs, President Manny Marcano discusses the rationale and plans for the new company.

by MIKE BUETOW

#### **MINIATURIZATION**

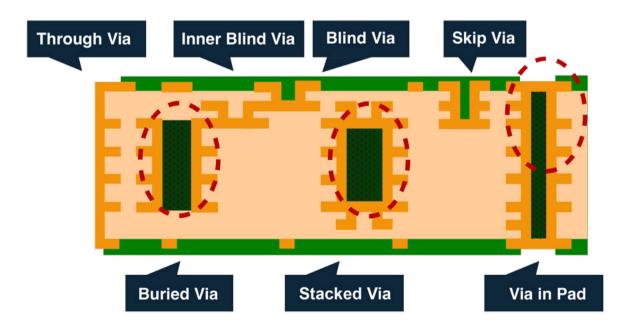

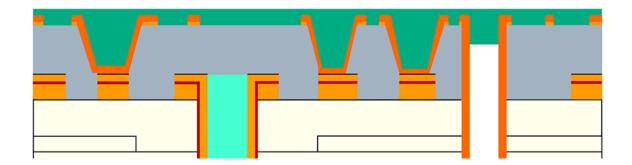

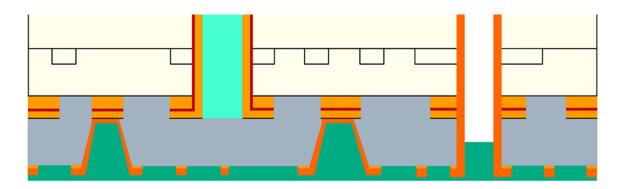

#### High-Density Interconnect Technology: An Overview

Production and assembly of HDI PCBs comes with unique technical challenges centered around reliability and quality. An overview of standards and best practices for designing and building HDI PCBs.

by AKBER ROY

#### **ASSEMBLY SERVICES**

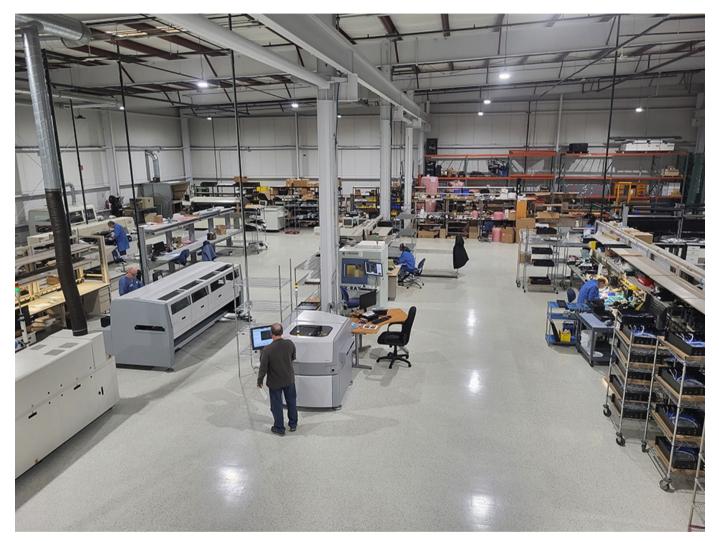

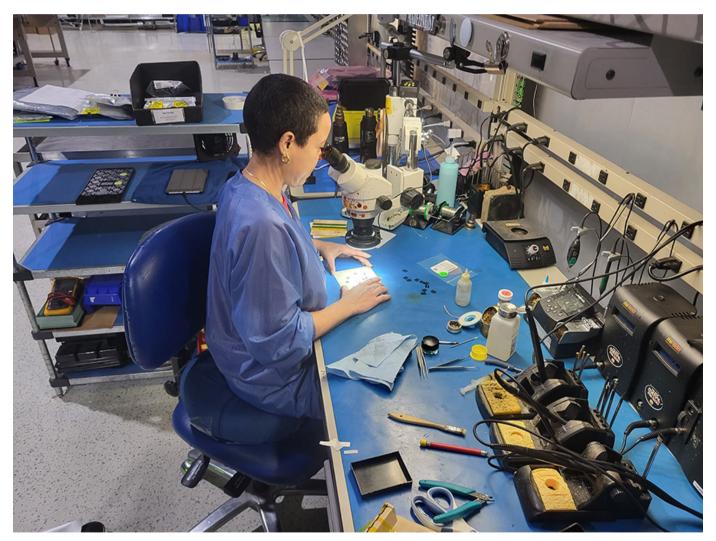

#### Windy City Tour

While not as well-recognized as the Silicon Valley, Chicagoland is another US hotbed of EMS activity. PCD&F/CIRCUITS ASSEMBLY visited a trio of area companies -Imagineering, BEST and BESTProto - each of which specializes in different niches but has recognized the need for responsiveness in a demanding environment.

**by TYLER HANES**

#### ON PCB CHAT (PCBCHAT.COM)

#### ENVIRONMENTALLY RESPONSIBLE / SUSTAINABLE CONFORMAL COATING with DR. CASSANDRA ZENTNER

PCB DESIGN SOFTWARE MARKET TRENDS with WALLY RHINES

THE SPINOFF OF ACCELERATED DESIGNS with MANNY MARCANO

PCB DESIGN with ZACHARIAH PETERSON

### TOP 3 REASONS TO PARTNER WITH IMAGINEERING INC.

### 2 35+ YEARS OF INDUSTRY EXPERTISE AND EXPERIENCE

### **3** FAST TURNAROUND WITHOUT COMPROMISING QUALITY

Some of the biggest brands in the world choose Imagineering for their printed circuit board fabrication and assembly

Whether you're looking for full turnkey services or PCB assembly that uses your parts, our PCB expertise gives you the highest quality printed circuit boards you need and the quick turnaround time you demand.

> Get an online PCB quote in minutes: www.pcbnet.com/quote/

www.pcbnet.com sales@pcbnet.com 847-806-0003 imagineering,inc.

ITAR Registered AS9100D/ISO 9001:2015 SAM Registered RoHS Compliant IPC Member

PCEA PO BOX 807 AMESBURY, MA 01913

#### PCEA BOARD OF DIRECTORS

Stephen Chavez, CHAIRMAN Justin Fleming, SECRETARY Gary Ferrari, CHAIRMAN EMERITUS

#### MEMBERS

Michael Buetow Tomas Chester Douglas Dixon Richard Hartley Scott McCurdy Anaya Vardya Susy Webb Eriko Yamato

#### PCEA.NET

#### THE PRINTED CIRCUIT ENGINEERING ASSOCIATION, INC. BRANDS:

| PUBLICATION PCD&F/Circuits Assembly | digital.pcea.net             |

|-------------------------------------|------------------------------|

| WEBSITES<br>PCD&F                   |                              |

| Circuits Assembly NEWSLETTER        | circuitsassembly.com         |

| PCB Update                          | pcbupdate.com                |

| PODCASTS<br>PCB Chat                | pcbchat.com                  |

| EVENTS                              |                              |

| PCB West                            |                              |

| PCB East                            | pcbeast.com                  |

| EDUCATION                           |                              |

| PCB2Day                             | pcb2day.com                  |

| PCEA Training                       |                              |

| Printed Circuit University          | printedcircuituniversity.com |

| AWARDS PROGRAMS                     |                              |

| Service Excellence Awards           | circuitsassembly.com         |

| NPI Awards                          | · · · · ·                    |

|                                     | pcdandf.com                  |

| DATABASE                            |                              |

| Directory of EMS Companies          | circuitsassembly.com         |

#### PRINTED CIRCUIT DESIGN & FAB pcdandf.com circuitsassembly.com

#### MANAGEMENT

#### PRESIDENT

Mike Buetow 617-327-4702 | mike@pcea.net VICE PRESIDENT. SALES & MARKETING

Frances Stewart 770-361-7826 | frances@pcea.net

#### PCD&F/CIRCUITS ASSEMBLY EDITORIAL

MANAGING EDITOR

Tyler Hanes 205-258-0067 | tyler@pcea.net

#### **COLUMNISTS AND ADVISORS**

Clive Ashmore, Peter Bigelow, Robert Boguski, John D. Borneman, John Burkhert, Jr., Stephen Chavez, Geoffrey Hazelett, Mark Finstad, Nick Koop, Alun Morgan, Susan Mucha, Greg Papandrew, Chrys Shea, Jan Vardaman, Gene Weiner

#### PRODUCTION

```

ART DIRECTOR & PRODUCTION

blueprint4MARKETING, Inc. | production@pcea.net

Nathan Hoeller | nathan@pcea.net

```

#### SALES

VICE PRESIDENT, SALES & MARKETING Frances Stewart 770-361-7826 | frances@pcea.net SENIOR SALES EXECUTIVE Will Bruwer 404-313-1539 | will@pcea.net

#### REPRINTS

sales@pcea.net

#### **EVENTS/TRADE SHOWS**

EXHIBIT SALES

Frances Stewart 770-361-7826 | frances@pcea.net

TECHNICAL CONFERENCE

Mike Buetow 617-327-4702 | mike@pcea.net

EVENTS MANAGEMENT

Jacqueline Bress 404-955-7675 | jacqueline@pcea.net

#### SUBSCRIPTIONS

PRINTED CIRCUIT DESIGN & FAB/CIRCUITS ASSEMBLY is distributed without charge to qualified subscribers. To subscribe, visit pcdandf.com or circuitsassembly. com and click on Subscribe. For changes or cancellations to existing subscriptions: subscriptions@pcea.net

PRINTED CIRCUIT DESIGN & FAB/CIRCUITS ASSEMBLY is published monthly by Printed Circuit Engineering Association, Inc., PO Box 807 Amesbury, MA 01913. ISSN 1939-5442. GST 124513185/ Agreement #1419617.

© 2024, Printed Circuit Engineering Association, Inc. All rights reserved. Reproduction of material appearing in **PRINTED CIRCUIT DESIGN & FAB/ CIRCUITS ASSEMBLY** is forbidden without written permission.

# OrCAD X

### NEXT GENERATION PCB DESIGN

THIS EVOLUTION OF PC3 DESIGN EXPANDS OUR SERVICES TO CREATE A TOOL THAT IS FASTER, MORE AUTOMATED, AND MORE CONNECTED THAN EVER. DESIGN FAST, CORRECT, CONNECTED.

GET STARTED TODAY >>

**EMA** Design Automation<sup>®</sup>

cadence°

# Today Middle School. Tomorrow the World.

IF YOU HAVE a child in Mrs. Dollas' eighth-grade class at the Rupert A. Nock Middle School in Newburyport, MA, odds are you are probably pretty steamed with me right now.

For those who aren't up to speed, here's why.

On a cold winter day in mid-January, I addressed her students about careers in electronics. About 20 teens gathered for the school's ongoing career exploration series (which as an aside, is a wonderful concept that all middle schools should adopt). I was invited to speak about my own career, but I quickly pivoted to the possibilities in tech that don't involve creating an app.

After asking for a show of hands from those who have been scolded by their folks for excessive video game playing – all of them – I then served them a counterargument: Play more!

My reason, I explained, is because video games – well, many of them – encourage students to use their imaginations. And while acknowledging their inherent addictiveness, I also believe they impart tremendous skills and subtle knowledge that will be useful to future generations of workers.

The first major trade show I attended was the Summer Consumer Electronics Show some 30 years ago, back when it was held in Chicago. There I saw the prototypes for HDTV and widescreen TVs, and more interesting, the first foldable screens.

I have to admit, nothing quite caught their attention more than the images of the devices that were common when I was their age. Seeing their faces as I showed the old floor TV models as large as a desk and the computer terminals the size of small ovens I grew up with was amusing. But it also reinforced the point that, as 13- and 14-year-olds, at least some of them are a scant eight years away from graduating college and facing the possibility of dreaming up and making the next round of electronics.

A Magnavox floor model similar to the one I grew up with. Fancy!

We are reminded, of course, that it takes a generation or more for most ideas to become mainstream. But fast forward to this year's CES, and among other innovations there were transparent TVs (thanks to LG and Samsung), foldable OLED PC monitors (Asus), and a portable rolling robot projector (Samsung again) that, well, you really have to see to understand what it is capable of.

Samsung's "transparent" TV, introduced this year.

Who but avid video game players would think of these things?

Of my cohort that January morning, two of them are already thinking in terms of engineering careers, but in my opinion what's more important is that none of them rules out this path. I took care to point out the many different ways there are to get here, and how many opportunities there are, regardless of one's particular skill set or interests. In other words, a lifetime in technology doesn't have to start with mad math skills.

Mentoring peers is great and important, but I'm a big proponent of talking to youth and helping them connect the dots. As the saying goes, if you want to see the future, take a look at your kids.

And if you agree that we need the next generation to consider careers in electronics design and manufacturing, are you doing what you can to encourage them?

mike@pcea.net @mikebuetow

P.S. Our condolences to the many friends and family of Michael Ford, who passed away Jan.27. Michael was a former columnist for PCD&F/CIRCUITS ASSEMBLY, a regular speaker at our conferences, a trusted advisor and a fantastically warm person. We will miss him.

MIKE BUETOW is president of PCEA (pcea.net); mike@pcea.net.

## Humidity Controlled Storage

J-STD Storage of PCBs & MSD Components

DRY CABINET STORAGE

XDry humidity-controlled storage cabinets are self-contained, low-maintenance storage systems. There is no need for nitrogen or compressed air, just plug into the wall and they are ready to go! XDry storage cabinets satisfy standards such as IPC/JEDEC J-STD-033 and IPC/JEDEC J-STD-020. The cabinet environment can be maintained from ambient to 1% RH, providing constant & stable storage at precisely desired RH levels.

XDry cabinets are the ideal solution for printed circuit board and moisture-sensitive component storage.

> HXD1-703-02 Small footprint, but high capacity

**Corporate Office** 3407 County Road 427 Anna, Texas 75409 USA

Phone: 214.296.4868

www.XDry.com

XD1-302-02 Competitively

Priced

HXD2-1106-01 Our largest heated

.

0

9,

dry cabinet

sales@XDry.com

💿 - 💿 💽 XDer 📅 🔢 🕄 🔍 🕤 👄 👄

### Synopsys to Acquire Ansys in \$35B Deal

SUNNYVALE, CA – Synopsys and Ansys in January announced a definitive agreement under which Synopsys will acquire its fellow ECAD provider for \$35 billion in stock and cash. The deal is expected to close in the first half of 2025.

Cadence Design Systems and Siemens also reportedly made bids for Ansys before Ansys agreed to the Synopsys sale, with Cadence kicking off the sales process after making an initial acquisition offer last fall, CNBC reported.

Ansys shareholders will own 16.5% of Synopsys following the merger, Synopsys CEO Sassine Ghazi said during a conference call after the announcement. The deal will be funded in part by \$16 billion of new debt, plus \$3 billion in cash.

Combining Synopsys' semiconductor EDA tools with Ansys' broad simulation and analysis portfolio will create a leader in silicon to systems design solutions, the companies said.

"The megatrends of AI, silicon proliferation and software-defined systems are requiring more compute performance and efficiency in the face of growing, systemic complexity," Ghazi said. "Bringing together Synopsys' industry-leading EDA solutions with Ansys' world-class simulation and analysis capabilities will enable us to deliver a holistic, powerful and seamlessly integrated silicon to systems approach to innovation to help maximize the capabilities of technology R&D teams across a broad range of industries. This is the logical next step for our successful, seven-year partnership with Ansys and I look forward to working closely with the talented Ansys team to realize the benefits of this combination for our customers, shareholders and employees."

"Since inception 37 years ago, Synopsys has been an innovation pioneer, central to world-

changing semiconductor advances in computation, networking, and mobility, and now enabling the new era of 'pervasive intelligence'," said Aart de Geus, executive chair and founder of Synopsys. "Joining forces with Ansys, a company we know well from our longstanding partnership, is the latest example of how Synopsys remains at the forefront. Our board and management team carefully evaluated our top strategic options to lead and win in this fast-growing new wave of electronics and system design. The technology-broadening team-up with Ansys is an ideal, value-enhancing step for our company, our shareholders, and the innovative customers we serve."

"For more than 50 years, Ansys has enabled customers to design, develop and deliver cuttingedge products that are limited only by imagination. By joining forces with Synopsys, we will amplify our joint efforts to drive new levels of customer innovation," said Ajei Gopal, president and CEO of Ansys. "This transformative combination brings together each company's highly complementary capabilities to meet the evolving needs of today's engineers and give them unprecedented insight into the performance of their products."

# GreenSource Nabs \$43M DoD Award for Fab Upgrades

WASHINGTON – The Department of Defense in late December announced an award of \$46.2 million to GreenSource Fabrication to enhance existing production capabilities at a manufacturing facility of state-of-the-art IC substrate, high-density interconnect (HDI) and ultra-high-density interconnect (UHDI), and advanced packaging.

The grant was made as part of the recently signed Defense Production Act Investment (DPAI) Program.

"Reshoring advanced packaging and assembly are essential to increase semiconductor supply chain security," said Dr. Laura Taylor-Kale, Assistant Secretary of Defense for Industrial Base Policy. "Expanding domestic production capability for printed circuit boards and advanced packaging is necessary to avert a shortfall that would severely impair national defense capability." The award will enable GreenSource to scale up engineering, tooling, and manufacturing operations to establish a dedicated facility for IC substrate fabrication for a high-mix, low-volume offering of advanced interconnect solutions. These domestic production capabilities for HDI, UHDI, IC substrates, and advanced packaging are critical enabling technologies for sixth-generation systems and applications, including for radar, electronic warfare, information processing, and communications.

### Siemens Adds Thermal Digital Twin Technology

PLANO, TX – Siemens Digital Industries Software has announced a new approach for sharing accurate thermal models of IC packages.

The main advantages of the new technology are protecting intellectual property, enhancing supply chain collaboration and accuracy of models for steady state and transient thermal analysis to enhance design studies, the company said.

Introduced in the latest updates to Simcenter Flotherm software for electronics cooling simulation from the Siemens Xcelerator portfolio, the Embeddable Boundary Condition Independent Reduced Order Model (BCI-ROM) technology permits a semiconductor company to generate an accurate model that can be shared with its clients for use in downstream high-fidelity 3-D thermal analysis without exposing the IC's internal physical structure.

MediaTek, a fabless semiconductor company specializing in systems-on-chip (SoC) for mobile, home entertainment, connectivity and IoT products, uses Simcenter Flotherm to drive efficiency in its collaboration with customers.

"Embeddable BCI-ROM is a great way to share our thermal models with our customers. It has several key features: easy generation, confidentiality, low error rate, and suitability for steadystate and transient applications," said Jimmy Lin, technical manager, MediaTek.

Today's electronics often have heat dissipation challenges that need to be resolved during

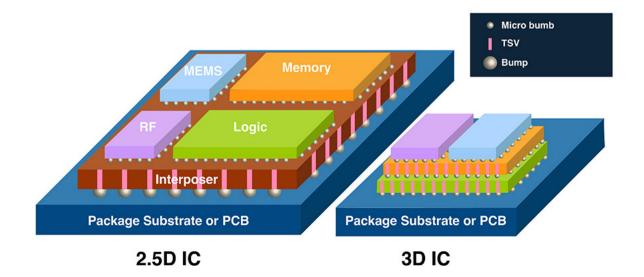

design due to higher power density influenced by the miniaturization of semiconductor packages and electronic systems, trends for thin-form consumer products, or demanding processing requirements. As a result, the need for more detailed thermal models to help solve thermal management design tasks is growing. Increasingly, modern IC package architectures such as 2.5-D, 3-D IC, or chiplet-based designs have highly complex thermal management challenges that require 3-D thermal simulation both during their development and during integration of IC packages into electronics products.

"Given electronics supply chain pressures and the growing complexity of IC packages, barriers to collaboration and thermal analysis efficiency during design must be eliminated where possible to support competitive development," said Jean-Claude Ercolanelli, senior vice president, Simulation and Test Solutions, Siemens Digital Industries Software. "Our breakthrough new technology enables accurate thermal models to be shared securely within the electronics supply chain without exposing sensitive intellectual property, allowing all parties to resolve thermal issues faster and bring advanced products to market more quickly."

### Cadence Acquires Invecas

SAN JOSE – Cadence Design Systems has announced the acquisition of Invecas, a provider of design engineering, embedded software and system-level solutions headquartered in Santa Clara, CA. Terms of the transaction were not disclosed. The acquisition is expected to be immaterial to Cadence's total revenue and earnings this year, the company said.

The acquisition brings a skilled engineering team centered in Hyderabad, led by Invecas CEO Dasaradha Gude, that has vast experience in delivering end-to-end system solutions with deep expertise in advanced nodes, mixed-signal, verification, embedded software, packaging and turnkey custom silicon production, Cadence said a release.

Invecas has served hundreds of customers across various verticals, including mobile, networking, hyperscaler and automotive, and in addition to Cadence's EDA solutions, the newly acquired company will also leverage and augment Cadence's IP portfolio to enable more comprehensive custom product solutions. "With complexity and challenges increasing due to the proliferation of AI, 2.5-D/3-D and chiplet designs, customers need access to experienced teams that can assist with bringing designs from ideation to production," said Boyd Phelps, senior vice president and general manager, Silicon Solutions Group, Cadence. "With the acquisition of Invecas, Cadence is able to scale our system design engineering offerings to support customers in critical high-growth verticals who are faced with the need to aggressively increase performance while tackling ever-increasing system-level complexity."

"Generational trends are accelerating the increases in design complexity and driving a customer need for skilled engineering talent that can assist with system design," said Dasaradha Gude, CEO, Invecas. "We are excited to join the Cadence team and to enhance the solutions available to customers, utilizing our core expertise to accelerate customer silicon and system development efforts."

### Simmtech Investing in Indian Semiconductor Fab

CHEONGJU, KOREA – South Korean PCB maker Simmtech has announced plans for a INR1,250 core (\$151 million) investment in the Indian state of Gujarat to support Micron's semiconductor plant being built in the state.

Simmtech CEO Jeffery Chun made the announcement at the 2024 Vibrant Gujarat Global Summit.

"Through the support of central and state governments, we are ready to make an investment in Gujarat which will create thousands of jobs," he said.

Last year, Micron announced plans to set up a semiconductor assembly and test plant in Gujarat with a total investment of \$2.8 billion.

Chun said the colocation investment with Micron mirrors a similar investment that the company previously made in China, and this investment will further India's goal to become a major player in the global semiconductor supply chain.

"We really look forward to further supporting our customers' supply chain, both in India and globally," he said. "And we will further enable India's domestic players to be part of the global supply chain ecosystem."

Simmtech ranked 21st on the 2023 NTI-100 list of the world's largest PCB fabricators, with reported revenue of \$1.3 billion in 2022.

### Orbic Electronics to Move Manufacturing from China to US

HAUPPAUGE, NY – Orbic Electronics Manufacturing has announced the launch of its Project Patriot initiative, which will move its manufacturing operation from China to New York's Suffolk County, bringing more than 1,000 new jobs to the area.

Orbic Electronics Manufacturing produces a range of connected devices, including smartphones, tablets and mobile hotspots.

"This initiative is a stride forward in our vision of a sustainable, job-creating future," said Mike Narula, President and CEO, Orbic Electronics. "Project Patriot is set to be a very exciting time in our company's history, and Suffolk County is the perfect location for the bulk of our work to advance the production of American-Made products and grow American manufacturing jobs. Having our products read 'Made in America' is a tremendous point of pride for us, and it will also allow our company to bolster the local economy, helping other vendors in Suffolk County succeed alongside us."

Orbic received an incentive from the Suffolk County Industrial Development Agency to lease and renovate a 70,000 sq. ft. building, which sits on a five-acre lot in Hauppauge, as part of a \$30.8 million investment. The investment into renovating the building and adding manufacturing technology is expected to achieve a mass production target of five million units per year and create more than 1,000 jobs in the next five years, the company said. **EP**

### Amber Enterprises Acquires Majority Stake in Ascent Circuits, Signs MoU with Korea Circuits

GURGAON, INDIA – Indian EMS provider Amber Enterprises, through its subsidiary Iljin Electronics, has acquired a 60% stake in PCB maker Ascent Circuits for an undisclosed sum.

India-based Ascent Circuits' clients include the Indian Space Research Organisation (ISRO), Bharat Electronics (BEL) and Bharat Heavy Electricals (BHEL), as well as several domestic and global automotive, telecom, and consumer electronics companies.

Amber, under the newly acquired Ascent Circuits, also signed a memorandum of understanding with South Korea's Korea Circuit to boost its PCB portfolio.

"This association between Amber and Korea Circuit will envelop the entire portfolio of PCBs required for various applications in India's electronics manufacturing growth story i.e. HDI (high density interconnect), flex, semiconductor substrate, multilayer, double-sided, (and) single-sided," the company said.

### Kontron Acquires Majority Stake in EMS Katek

LINZ, AUSTRIA – Kontron has agreed to acquire around 60% of the shares in Katek in a bid to expand its portfolio of green energy solutions and the aerospace segment.

The transaction, in which Kontron is acquiring 8,587,138 shares in Katek for a purchase price

of  $\in$ 15 (\$16.30) per share from primary shareholder Primepulse, is expected to be completed by March pending regulatory review, Kontron said in a release.

Katek offers electronics manufacturing and products for solar energy and e-mobility. The company had revenue of more than  $\notin$ 750 million (\$815.2 million) in 2023, and has more than 3,200 employees in locations across Europe, Asia and North America.

The aim of the acquisition is to expand Kontron's portfolio with smart solutions for renewable energies and other industries, the company said, and to achieve this, Katek's products will be upgraded with Kontron's software expertise and IoT connectivity – enabling the products to become more secure, have firewall functionality, be able to connect to complex grids and be maintained remotely. The merger expands Kontron's "Software + Solutions" segment to include the future-oriented "GreenTec" division.

"With the acquisition of Katek SE, we are expanding our presence in the high-growth area of clean energy solutions in a targeted manner and also strengthening the Aerospace division at Kontron with the Katek subsidiary NexTek," said CEO Hannes Niederhauser. "The clean energy sector holds considerable potential for the future. Upgrading with Kontron software will increase gross margins by around 5% in the medium term, thereby increasing profitability at Katek as well."

### Neways Acquires Microsystems Firm Sencio

SON, NETHERLANDS – Neways in January announced the acquisition of Sencio, a microsystems company based in Nijmegen, Netherlands, that specializes in advanced packaging for smart sensing and actuation applications.

The acquisition solidifies Neways' position in microelectronics technology, the company said in a release. Sencio will continue to operate under the brand Neways Advanced Microsystems and operate out of its current facilities in Nijmegen.

"Over the past years Neways has invested significantly in its technology position, that allows

us to act as innovation partner for the most demanding customers in the industry," said Hans Büthker, CEO, Neways. "Through the acquisition of Sencio we further strengthen our market position in microelectronics and are able to offer a broader suite of integrated services to both Neways' and Sencio's customers. We welcome the Sencio team and are looking forward to our joint journey forwards."

"I am excited to become part of the Neways team and continue offering our technology with a large part of the dedicated and specialized Sencio team," said Sencio CEO Oliver Maiwald. "Joining forces with Neways enables us to offer a complete suite of advanced microelectronics services to a broad set of customers that can benefit from advanced packaging for smart sensing and actuation applications."

# Inission Announces Acquisition of AXXE

KARLSTAD, SWEDEN – Swedish EMS provider Inission has expanded its presence in southern Norway with the acquisition of AXXE. The companies signed an agreement for the sale on Jan. 17, and the deal closed on Jan. 31.

According to the agreement, Inission will pay NOK27 million (\$2.6 million) for 50.1% of the shares in AXXE, which is five times the average EBITDA for 2021-23. Inission will further pay six times the average EBIDTA from 2024-26 for the remaining 49.9% of AXXE.

AXXE has a portfolio of customers in several different segments such as marine, communications and IoT and industrial, and has 46 employees located in Halden, Norway. In 2022, AXXE had sales of NOK138 million (\$13.1 million) and EBITDA of NOK8 million (\$759,000).

"We are extremely happy to see Inission expand in Norway through the acquisition of AXXE," said Erik Dragset, CEO, Inission. "The company is one of the best-known EMS companies in the country and we look forward to a strong collaboration. With Inission's and AXXE's combined capacity and industry knowledge, we can offer our customers both ground-breaking solutions and world-class customer service."

"As an EMS company in electronics manufacturing, we are one of the oldest and most experienced in our field," said AXXE CEO Øystein Back. "We have worked with the production and assembly of complex electronics together with many of our customers for more than 17 years. By combining our strengths with Inission, we can take care of our customers more efficiently, offer a wider range of services and develop our business in a completely new way. This ensures that we meet the growing needs of all sectors of the electronics industry."

### LCY Group Signs \$9.5M Deal with Nippon Denkai

TAIPEI – Taiwan's LCY Group has signed a business and capital alliance agreement with Nippon Denkai's US electrolytic copper foils subsidiary to offer a \$9.5 million loan to support collaborations and share experiences in operations and expansions in the US.

In addition to the loan offered by LCY Group, the two companies have signed a license agreement under which LCY Technology will have access to Denkai's technology license. Under the agreement, LCY and Denkai will be able to complete and expand geographical customer portfolios and strengthen technological cooperation in rigid and flexible boards as well as high-functioning fields (high-frequency, high-density mounting, etc.), LCY said in a release.

The partnership aims to enhance the production flexibility of both parties in manufacturing high-end PCB copper foils, which are used in packaging substrates, 5G and advanced driver assistance systems (ADAS) applications in Taiwan, China and the global market. LCY said it believes that the combined technical expertise, product portfolio and rich customer experience of both sides will help Denkai Group accelerate the realization of its mid- to long-term goals, and the collaboration aims to maximize production and sales synergies through accelerated sales growth of specialized PCB copper foil.

### Foxconn Establishes EV Production

### Business in China

TAIPEI – Foxconn Technology Group has established an electric vehicle business in Zhengzhou, China, amid declining smartphone sales.

The new firm, Foxconn New Energy Automobile Industry Development, was founded in Zhengzhou – also home to Foxconn's 200,000-employee iPhone factory – with a registered capital of 500 million yuan (\$70 million), according to public records. Its business covers car component manufacturing and development, motor production and NEV sales, among other areas.

Foxconn said the new venture belongs to Foxconn Innovation Industry Development Group and aims to sharpen the company's focus on the electric vehicle industry, according to the South China Morning Post.

### Dixon Factory Searched by Indian Government

NOIDA, INDIA – Dixon Technologies has announced a search of one of its subsidiary's manufacturing facilities here by India's Directorate of Revenue Intelligence.

In a regulatory filing, Dixon said the DRI searched the factory regarding the classification of the raw material imported for manufacturing one of the products. The company said the search took place on Jan. 17, but did not specify the product or the raw materials that were searched.

Dixon said the search should not have a material impact on the company's operations, and it is cooperating with the investigation.

"The issues raised by the DRI are interpretational in nature and we stand committed to defend our interpretation using all recourse available to us. We have extended full cooperation to the DRI, including providing complete information in a timely manner," the

### DSL Launches In-House Assembly Service

**LETCHWORTH GARDEN CITY, UK** – DSL – Electronic Manufacture has established an inhouse PCB assembly service to bring design and manufacturing under the same roof.

The company, which has specialized in electronic design services during its history, said it first initiated the plans in the summer of 2023, after finding that the scarcity of components made it nearly impossible to produce PCB assemblies, and if they could be obtained, the costs were exorbitant.

"We found ourselves in a difficult position, trying to justify the significant price increases imposed by our outsourced manufacturing partners without any valid justifications ourselves," the company said in a release. "Moreover, we faced numerous manufacturing issues, including costly mistakes, especially considering the high prices of these components. Once again, DSL was left in a compromising position, disappointing our valued clients through no fault of our own. We reached a breaking point and decided that enough was enough."

After conducting research on the necessary equipment and manufacturers/models available, the company opted for a fully automated SMT assembly line, plus a 3-D automated optical inspection machine, and it revamped its entire production area by installing dedicated benches for through-hole assembly. Its production manager had also previously managed a contract electronics manufacturer in a past role, and with the support of its in-house design engineering team and the recruitment of skilled hand soldering technicians, DSL said it was well-prepared for the addition of assembly services.

The company said it will be fully equipped to launch its manufacturing capability by January.

#### ÷P

### Cicor Closes STS Defence Acquisition

BRONSCHHOFEN, SWITZERLAND – Cicor Group has successfully closed the acquisition of 100% of the shares of the UK-based STS Defence announced in October 2023.

With the acquisition, Cicor adds a specialist in the design, manufacture and assembly of equipment and systems, as well as the integration and maintenance throughout the equipment's life cycle. STS Defence employs around 150 people in the south of the UK and generated sales of GBP27.5 million (\$35 million) in the fiscal year ended Jun. 30.

Cicor said it is committed to continue providing engineering support and manufacturing services from the existing STS Defence site under the current management team.

#### BRIEFS

### PCD&F

Altair welcomed CADY to the Altair Partner Alliance.

**Aohong Electronics** announced plans to raise up to RMB580 million (\$81 million) for a production base project in Thailand.

**Aspocomp** announced the beginning of negotiations on possible temporary and permanent layoffs in Finland.

CML Micro acquired MwT, an MMIC and mmWave supplier based in California.

**Excellon** opened a new manufacturing facility in Paramount, CA.

**Icape** announced the completion of a €47 million (\$51 million) financing package.

Jove PCB expects its new production facility in Thailand to open in June.

MacDermid Enthone Industrial Solutions announced the acquisition of All-Star Chemical Company's surface finishing and cleaning chemical solutions.

**Nanya Technology** announced a 15-month high revenue of NT\$3.16 billion (\$102 million) for December.

**PCBPit** is extending its specialized services in PCB prototype manufacturing, fabrication and assembly.

**TTM Technologies** donated \$20,000 to the international humanitarian organization, Rise Against Hunger, through its TTM Chair of Community Service

Award.

**Zhen Ding Technology** held a groundbreaking ceremony for its \$250 million production facility in Thailand. **=P**

### CA

**Alan Anderson Manufacturing** invested £2 million (\$2.5 million) in PCBA production equipment, including surface mount and conventional assembly, selective soldering, conformal coating and 3-D AOI and x-ray inspection.

Arch Systems announced a three-year strategic collaboration with Jabil.

**Avalon Technologies** is now a strategic manufacturing partner for India's **Center for Development of Advanced Computing**.

**Blue M** announced the shipment of a Low Oxygen Class A oven to the medical industry.

**Cloud Network Technology**, a subsidiary of **Foxconn**, will increase its investment in **Ingrasys Technology Mexico** by \$10 million to expand its server assembly business in the country.

Creation Technologies opened a new 150,000 sq. ft. EMS facility in Newark, NY.

**Critical Manufacturing** was listed in the Deloitte "Technology Fast 50," which recognizes and profiles the fastest-growing public or private technology companies in a specific region.

Danutek opened a new facility in Timisoara, Romania.

**East West Manufacturing** will close its facility in Youngsville, NC, in March and lay off 107 workers.

**Foxconn** has injected Rs 461 crore (\$55.3 million) into Foxconn Precision Engineering in Bengaluru and signed a Mandarin-language education project MOU with four tertiary institutions in India aimed to deepen industry-academia ties and incubate future talent.

Hanza is building a new 8,800 sq. m. factory section in Töcksfors, Sweden.

Horizon Sales will distribute Aven's optical inspection tools.

HyRel Technologies appointed Horizon Sales as its representative in the Midwest.

Jabil opened a new 1 million sq. ft. plant in Chihuahua, Mexico.

Koh Young Technology is expanding into the medical robot business.

**Kübler High Tech Solutions** named **SMarTsol Technologies** exclusive sales representative for Arcadia in Mexico.

LG is planning to bring some operations to West Virginia.

**Plexus** received notification that its Chinese subsidiary, **Plexus Xiamen**, will be removed from the Bureau of Industry and Security's Unverified List.

**Redarc** purchased a factory in Adelaide, Australia, to house staff spearheading its move into the defense and space sectors.

**Renesas** is acquiring **Transphorm** in a \$339 million deal to leverage its GaN expertise in power electronics.

**Scanfil** signed a multi-year agreement to produce **BrainCool** systems and components.

Silicon Mountain purchased an RO1 cobot robotic arm.

SMTXtra named Performance Technologies Group its representative for the

region spanning from Virginia to Maine.

**StenTech** opened a new facility in Clearwater, FL, and expanded its parts division in the US and Canada.

**Rocka Solutions** announced a strategic partnership to distribute **Weller Tools'** equipment.

Swiss electronics manufacturer Veratron has entered the Romanian market.

Vitrox opened a new office and demo center in Texas.

**Quectel Wireless Solutions** announced a collaboration with **Syrma SGS Technology** to facilitate the manufacturing of modules in India.

**Taliang Technology** will be stepping up its presence in the chipmaking industry, which presently contributes 10% of the company's overall revenue.

**Trueview** is expanding its electronics manufacturing plant for interactive flat panel displays in India.

### Measure PCB Surface Finishes ENIG, EPIG, EPAG & ENEPIG

Xray

- XRF with Automated X-Y Table

- Increased Throughput

- Improved Reliability

- IPC 4552 B & IPC 4556

Measuring Made Easy®

www.fischer-technology.com | info@fischer-technology.com | 860.683.0781

#### AROUND THE WORLD

#### PEOPLE

### PCDF

Antti Ojala

Pekka Holopainen

Avi Avula

Katarina Roy

Amjad Obeidat

Aspocomp named **Antti Ojala** chief commercial officer and **Pekka Holopainen** chief operating officer.

Methode Electronics appointed Avi Avula president and CEO.

Summit Interconnect named **Alfred Macha** vice president and general manager, Santa Clara facility.

Uyemura hired Katarina Roy as technical service engineer.

Waymo named **Amjad Obeidat, Ph.D.** to head Sensing & Perception Systems Engineering.

CA

Marlene Natale

Cliff Talbot

Taylor Wang

Walter Wang

Brett Larsen

Patrick Prondzinski

Don Dennison

Ray Page

Lu Anne Green

Vince Libercci

Benjamin Smith

Dan-Mar named Anthony Bellitto senior quality systems manager.

Indium promoted **Marlene Natale** to senior manager corporate quality, **Cliff Talbot** to senior quality engineering technician, **Taylor Wang** to associate director, China sales, and **Walter Wang** to associate director, operations.

Keytronic appointed **Brett R. Larsen** to succeed **Craig D. Gates** as president and CEO, effective June 30.

Kimball Electronics promoted **Patrick Prondzinski** to vice president of new business development.

Kübler named **Don Dennison** of PIT Equipment Services sales representative for Arcadia in the Northeast US.

Libra Industries appointed **Ray Page** chief financial officer.

MicroCare appointed **Lu Anne Green** COO and **Vince Libercci** national sales manager.

SelecTech appointed **Benjamin Smith** sales director.

VJ Electronix named Clint Buldrini New England sales representative. 🚝 P

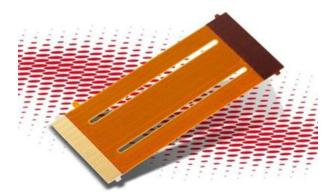

### Support For Flex, Rigid Flex and Embedded Component Designs Now Available.

DownStream's CAM350 and BluePrint-PCB support importation and visualization of PCB designs containing Flex, Rigid Flex or Embedded components. Visualize designs in both 2D and 3D, and easily document complex Flex or Rigid- Flex Stack-Ups for submission to PCB Fabricators.

- Import and Visualize Flex, Rigid-Flex and Embedded Component Designs

- 3D Visualization to Validate PCB Construction and Component Assembly

- Manage Variable Stackup Zones for Rigid-Flex Designs

- Easily Create Custom Flex or Rigid-Flex Fabrication and Assembly Documentation

- Use DFM analysis to analyze a flex or rigid-flex design for potential fabrication or bend related defects

Use Stack Up Visualizer and Blueprint's Rigid-Flex Stackup template to easily manage and document rigid-flex stackups.

A rigid-flex design in 3D. Shown with layers spread to improve visualization of the layer stackup. Use Rigid-Flex and Inter-layer DFM analysis to analyze flex and rigid-flex designs.

For more information visit downstreamtech.com or call (508) 970-0670

### PCB East 2024 Conference Registration Open

**PEACHTREE CITY, GA** – Registration for the technical program for PCB East 2024, featuring more than 75 hours of in-depth electronics engineering training, is now open.

Rick Hartley, Susy Webb, Tomas Chester and Zach Peterson are among the headliners of this year's conference. It will be held June 4-7 at the Boxboro Regency Hotel and Conference Center in Boxborough, MA. It features classes for every level of experience, from novice to expert.

The scope of classes ranges from basics on design engineering and circuit grounding, to DDR5 routing, impedance characterization, controlling noise and EMI, thermal management, board stackups and design for assembly.

More than half the presentations are new to the PCEA, including ones on SMT equipment validation, medical wearable device compliance, flex design, AI in electronics, and signal integrity/power integrity.

"Attendance more than doubled in 2023, showing both the vibrancy of the East coast electronics ecosystem and the need for topnotch technical training," said Mike Buetow, conference director, PCB East. "This year's event offers an array of experts in printed circuit design engineering and manufacturing, and a new emphasis on assembly."

Registration is now open for both the technical conference and the exhibition at pcbeast.com.

Registrants who sign up by May 3 can take advantage of the Early Bird Special discounts for the conference.

The program was developed by the PCEA Conferences Task Group from more than 60 abstracts submitted. The task group is made up of nine industry veterans with more than 270 years of cumulative experience in the printed circuit industry, chaired by Troy Hopkins.

### PCEA Announces Upcoming Webinar on IMS

PEACHTREE CITY, GA – Printed Circuit Engineering Association (PCEA) this month will hold a special member webinar on high-performance PCB materials for thermal management.

On Feb. 27, Chad Wood will deliver a one-hour talk on thermal IMS (insulated metal substrate). The term "IMS" refers to PCBs built on a metal (typically aluminum but also copper), which acts as a thermal substrate, while the dielectric adhesive (prepreg) provides high thermal transfer from the components while maintaining dielectric insulation. They can be used to replace direct bonded copper (DBC) substrates for power modules and devices.

The webinar takes place Feb. 27 at 1 p.m. EST. Register at https://attendee.gotowebinar.com /register/8917502632251720287. =

### Special Panel to Debate Al in Electronics

PEACHTREE CITY, GA – As use of artificial intelligence in electronics design and

manufacturing becomes a discussion point, it recalls a similar debate from 40 years ago on the impact of a new technology that promised to disrupt the industry norms of that era. On March 6, a special panel convened by PCEA will participate in a webinar where they consider the actual intelligence in these tools, and the ways – and how soon – they might impact the industry. (To register for the webinar, click here.)

Phil Marcoux, who is credited with installing the surface mount line in the US, will moderate the panel. He writes:

I was blessed to be part of helping facilitate the acceptance of something called SMT, having co-founded and managed one of the first design and manufacturing companies devoted to SMT and trying to employ as much automation (and I guess early AI), as possible.

Starting in 1982 industry sponsored panels (no webinars in that day!) comprised of several early adopters debated the need for collaborative data gathering to create the fundamental needs to successfully design and manufacture using the heretical idea of soldering components onto the surface of pcbs rather than in holes.

Getting the experienced practitioners to share data was worse than pulling teeth. It wasn't until certain departments of the US government and two persuasive individuals in the IPC (Ray Pritchard and Dieter Bergman) coerced a gathering of 20 C-level executives that cooperation was needed. This led to the creation of The Surface Mount Council, of which I was a charter member and served for its entire 12 years.

Handing off its duties in 2001 to a more international effort led by IPC, the Council published more than six white papers. The SMC has also participated in the SMART, SMI, IPC SMEMA Council's APEX and SMTAI technical conferences and initiated and sponsored joint standards for new technologies, including TR-001, "An Introduction to Tape Automated Bonding Fine Pitch Technology," J-STD-012, "Implementation of Flip Chip and Chip Scale Technology" and J-STD-013, "Implementation of Ball Grid Array & Other High Density Technology."

Early in the SMC effort it was apparent that gaining industry wide acceptance depended on data sharing, particularly for design guidelines, especially land patterns,

metallization standards for components, and workmanship criteria. Without common knowledge of these the SMT effort would continue to flounder.

I think the same will happen with the effort to incorporate problem solving, process control, and early warning power, among other benefits, of the use of AI-assisted tools.

In addition to the challenge of creating adequate databases of information necessary for the intelligence in AI, we have the issue of how to communicate these data without compromising the data owner's needs. And just as with SMT, there's a large concern about the impact on jobs. If the history of SMT teaches us anything, it's that AI can help the industry create new and more productive jobs.

On March 6, one of the first gatherings of experts in AI for electronics will be held. Will this be the start of a new inflection point in the electronics industry, leading to the creation of many new products exceeding the marvels of those resulting from the use of SMT?

Attend and be a part of history. 🚝 P

#### PCEA CURRENT EVENTS

#### **CHAPTER NEWS**

**New England.** The chapter plans a kickoff meeting on May 2, probably in the Andover (MA) area. Among the planned speakers are Gopu Achath of EMA Design Automation on supply chain-driven circuit design and Paul Yang of Jove PCB on embedded inductors. Contact Mike Buetow at mike@pcea.net for details.

Silicon Valley. The next chapter meeting is Feb. 14 from 11:30 to 1:30 PST. The meeting topic is Design Essentials to Maintain Signal Integrity, presented by Amit Bahl of Sierra Circuits. The meeting will be held both in-person at Sierra Circuits and online (Zoom). To attend in person, contact Bob McCreight for more information; bob.mccreight@outlook.com. To attend via Zoom, click here.

**PCEA Training.** Upcoming five-day training classes for printed circuit engineers, layout professionals, and other individuals currently serving in the design engineering industry or seeking to get into it will take place on the following dates:

- April 5, 12, 19, 26, and May 3

- June 14, 17, 21, 24, 28

These instructor-led classes are held online and cover the gamut of printed circuit design engineering, from layout, place and route to specifications and materials to manufacturing methods. Schematic capture, signal integrity and EMI/EMC are also part of the comprehensive program.

Registration fees include the 400-page handbook, *Printed Circuit Engineering Professional,* authored by Michael Creeden, Stephen Chavez, Rick Hartley, Susy Webb and Gary Ferrari. The course includes an optional certification exam recognized by PCEA.

For information about the instructors of the course and authors of the course material, visit pceatraining.net/instructors-authors.

For information about the course overview, class format, and materials to prepare in advance for the class, visit pceatraining.net/course-overview.

venteclaminates.com

### VT-5A2 - Superior thermal performance where size and simplicity matter

**Thermally Conductive Laminate & Prepreg**

With eight times the thermal conductivity of standard FR4, VT-5A2 handles the heat from high-power EPS and motor drives, displays, power circuitry and multi-layer constructions.

### **Key Features:**

Thermal Conductivity: 2.2 W/mK Tg: 190°C MOT: 150°C T260 >60 minutes

### **Get in Touch**

#### **EMEA**

Peter Coakley +44 7976 946 138 peter.coakley@ventec-europe.com

#### Americas

Pesh Patel +1 714 683 7825 pesh.patel@ventec-usa.com

#### Asia

Shawn Peh +65 96 279 906 shawn@ventec.com.cn

#### **Germany / DACH**

Jürgen Knörchen +49 173 421 4625 juergen.knoerchen@ventec-europe.com

## PCB Design Tool Sales Set Record in Q3

MILPITAS, CA – Sales of design software for printed circuit boards and multichip modules rose 23.6% to \$426.1 million in the third quarter 2023, the ESD Alliance announced in January.

The four-quarter moving average, which compares the most recent four quarters to the prior four, rose 14%.

Electronic design automation industry revenue rose to \$4.7 billion, an increase of 25.2% from 2022, and the four-quarter moving average rose 13.8%.

"Electronic design automation (EDA) reported record revenue growth in Q3 23," said Walden C. Rhines, executive sponsor of the SEMI Electronic Design Market Data report. "This was the highest overall growth since Q4 1998. The computer-aided engineering, IC physical design and verification, printed circuit board and multichip module, and semiconductor intellectual property categories reported double-digit growth. Further, all geographic regions reported substantial growth."

| Q3 2023 PCB Design Software Revenue |          |      |       |       |        |        |          |

|-------------------------------------|----------|------|-------|-------|--------|--------|----------|

|                                     | Americas | EMEA | Japan | APAC  | Q3 '23 | Q3 '22 | % Growth |

| PCB/MCM software                    | 171      | 85.4 | 40    | 129.7 | 426.1  | 334.7  | 23.6     |

| In \$ millions                      |          |      |       |       |        |        |          |

The companies tracked in the EDMD report employed 59,737 people globally in the third quarter, a 10.6% jump over 2022 and up 1% sequentially.

By product category, CAE revenue increased 22.4% to \$1.7 billion and the four-quarter moving average increased 16.7%. IC physical design and verification revenue surged 45.3% to \$904.5 million, with the four-quarter moving average increasing 29%.

Semiconductor intellectual property (SIP) revenue increased 22.1% to \$16 billion. The fourquarter SIP moving average rose 5.3%. Services revenue slipped 3.9% to \$138.3 million, and the four-quarter Services moving average rose 6%.

By region, the Americas procured \$1.98 billion of electronic system design products and services in Q3, a 22.8% jump. The four-quarter moving average for the Americas rose 11.2%. Europe, Middle East, and Africa (EMEA) came in at \$551.1 million, up 21.5%. The four-quarter moving average for EMEA grew 13.4%. Japan's demand rose 30.5% to \$309.3 million, with the four-quarter moving average rising 9.4%. And Asia Pacific procured \$1.86 billion, up 28.1%, with the four-quarter moving average growing 17.8%.

|                                            | % CHANGE |       |                   |      |

|--------------------------------------------|----------|-------|-------------------|------|

|                                            | SEP.     | OCT." | NOV. <sup>p</sup> | YTD  |

| Computers and electronics products         | 0.7      | 0.1   | 0.7               | 1.9  |

| Computers                                  | -2.9     | 5.0   | 4.8               | 13.1 |

| Storage devices                            | -2.1     | 1.0   | -1.0              | 13.3 |

| Other peripheral equipment                 | 3.4      | -5.2  | 2.6               | 22.9 |

| Nondefense communications equipment        | 1.5      | -1.0  | 0.5               | -1.8 |

| Defense communications equipment           | -1.5     | 4.0   | -2.4              | 2.8  |

| A/V equipment                              | -12.7    | -7.8  | 0.2               | 16.4 |

| Components <sup>1</sup>                    | 2.8      | -2.5  | 1.7               | 2.4  |

| Nondefense search and navigation equipment | 1.2      | 0.0   | 0.6               | 1.2  |

| Defense search and navigation equipment    | 0.2      | 1.1   | 1.6               | 4.5  |

| Electromedical, measurement and control    | 0.0      | 2.3   | -0.2              | 1.2  |

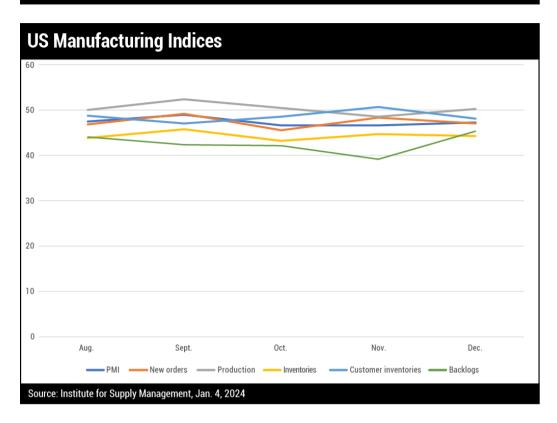

| Key Components                  |      |      |      |      |      |

|---------------------------------|------|------|------|------|------|

|                                 | AUG. | SEP. | OCT. | NOV. | DEC. |

| EMS book-to-bill <sup>1,3</sup> | 1.27 | 1.27 | 1.23 | 1.22 | 1.20 |

| Semiconductors <sup>2,3</sup>                                                                                    | -6.8% | -4.5% | -0.7% | 5.3%  | TBA   |

|------------------------------------------------------------------------------------------------------------------|-------|-------|-------|-------|-------|

| PCB book-to-bill <sup>1,3</sup>                                                                                  | 1.00  | 1.01  | 0.97  | 0.97  | 0.90  |

| Component sales sentiment <sup>₄</sup>                                                                           | 90.3% | 86.7% | 88.8% | 83.3% | 83.3% |

| Sources: <sup>1</sup> IPC (N. America), <sup>2</sup> SIA, <sup>3</sup> 3-month moving average, <sup>4</sup> ECIA |       |       |       |       |       |

### Hot Takes

Worldwide **semiconductor revenue** in 2023 totaled \$533 billion, a decrease of 11.1% from 2022. (Gartner)

Global **smartphone shipments** declined 3.2% year over year to 1.17 billion units in 2023. (IDC)

North American **electronics manufacturing services shipments** in December rose 1.3% over last year and 6.2% sequentially. Bookings fell 7% year-over-year and increased 2.3% sequentially. (IPC)

Worldwide IT spending is expected to rise 6.8% year-over-year to \$5 trillion in 2024. (Gartner) The downswing of **DRAM contract prices**, which had lasted for eight consecutive quarters since Q4 2021, reversed in the December quarter. (TrendForce)

A reduction in input tariffs could increase **India's smartphone exports** to \$39 billion by 2027 from \$11 billion in 2023. (India Cellular and Electronics Association)

Global investments in **space startups** jumped 31% sequentially in the fourth quarter. (Space Capital)

Despite facing a traditional low-demand season, buyers are continuing to increase their purchases of NAND flash products to establish safe inventory levels. (TrendForce)

North American **PCB shipments** fell 18.3% in December from a year ago. Bookings dropped 28.7% from 2022 and were down 14.1% compared to November. For the year, orders fell 10%. (IPC)

About 4,500 tech industry jobs have been lost so far in 2024, and tech job unemployment is 2.3%. (Layoffs.fyi, CompTIA)

The medium-term outlook is for **continued resilient expansion in the APAC** region, with robust domestic demand in many Asian emerging economies, supported by their global competitiveness in the electronics manufacturing supply chain. (S&P Global Market Intelligence)

**Passive component manufacturers** predict a market rebound after the second quarter and into the second half of this year. (DigiTimes)

Electronics industry sentiment took a dip in December with new order, shipment, and backlog indices falling, with only capacity utilization index holding steady. Despite the dip, overall demand sentiment remained in positive territory. (IPC)

Worldwide PC shipments plunged 14.8% year-over-year in 2023, totaling 241.8 million units. (Gartner)

Shipments of traditional PCs fell 2.7% to 67.1 million PCs in the fourth quarter. (IDC)

The French government is looking to create 18,000 jobs in the electronics sector in 2024. (France Ministry of the Economy, Finance and Industrial and Digital Sovereignty and the Ministry of Higher Education and Research)

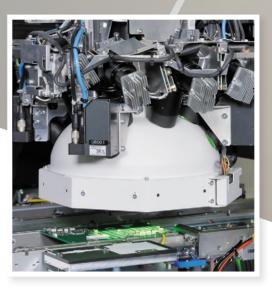

# **Eliminate defects with Yamaha's Al enhanced AOI**

- + Fastest 3D Automated optical inspection on the market today!

- + Resolution for narrow pitch 0201mm devices.

- + New co-axial lighting system for finding defects in reflective surfaces.

- + New camera and projector system offers improved inspection capability.

- + New unified YR platform machine interface.

Yamaha can meet the challenges of almost any product that is on the market today. Don't miss the opportunities for these new technologies!

Learn more at <u>www.yamaha-motor-im.com</u> For inquiries: <u>y-sales@yamaha-motor.com</u>

### Striking a Balance

The tech industry – and world at large – could use some moderation.

MODERATION AND BALANCE seem in short supply throughout the world these days. Between war on two sides of the globe and political extremes in vogue all over, the proverbial pendulum is swinging wildly, rarely landing in the center. And business and industry are no exception to current trends.

In business and especially technology, the hot area is everything artificial intelligence (AI). Whether hardware or software, AI is the holy grail de jour. The regulatory environment is similarly out of balance. With security leaks, loss of privacy and potential pirating that could lead to everything from automobiles to aircraft and even weapons being manipulated by the "bad guys," layers of regulations, standards, audits and inspections have taken off in every segment of industry. Again, balance and moderation have given way to extremism.

In fact, industry has never needed balance and moderation more than now. "Reasonable" and "pragmatic" are two words that should be applied across a multitude of areas.

Technology could use a healthy dose of pragmatic balance. Take, for instance, the abandoning of gasoline vehicles for electric. Is recharging an electric vehicle's battery by plugging into an already overly taxed electric grid really the answer? Is it safer when a vehicle's controls reside on a touchscreen display out of the driver's typical line of vision rather than utilizing buttons and knobs closer to the hands on the wheel? And on a thousand-mile trip how many hours will be required to recharge the vehicle? Maybe a more balanced approach is to encourage small cars with energy efficient gasoline engines, hybrid vehicles and limiting the size/weight of energy inefficient SUVs to reduce owners' costs as well as be environmentally better.

Ditto the quest for AI. Maybe those efforts should instead be focused on improving individual education – especially with a STEM curriculum. Or focusing on a reasonable immigration policy so all those flocking to a country can be assimilated into the workforce to fill manufacturing jobs for which it is so difficult to find applicants. I would hate to think that the search of AI ends up finding artificial stupidity!

Security – especially cybersecurity – is another area requiring balance and pragmaticism. Adding protocols, two-factor authentication (2FA) and other "safeguards" only works if the likes of Microsoft, Apple, etc., better manage how and when they issue software updates to make sure they are both secure and compatible with the myriad of other software they interact with. Education is also needed so employees understand what they should and should not do when using a computer or a "secure" network! Finally, if the security protocol is not understandable and easy for non-IT employees to use, dangerous workarounds *will* occur. Security protocols are no place to deploy a Rube Goldberg approach.

Individuals, or more to the point, employees, is another area in need of balance, moderation and reasonableness. Young folks need to be taught that when they have a job, especially a career job in manufacturing, they need to show up on time every day. Not being in the "mood" isn't going to cut it. My guess is that all the people around the world trying to emigrate to a new country would be happy for any job where they must show up on time, all the time! Ditto thoroughness. Basic training in public schools should include "GAS" training, which is "Give A Sh\*t!"

No matter the career or job pursued, if employees do not care, do not perform to the best of their abilities and do not strive for perfection, they will not be successful. If employers explicitly communicate to applicants the expectation that the applicant be reasonable in their requirements, balanced in how they interact with coworkers and pragmatic in how they approach the job, all will have a greater possibility for mutual success.

Expectations could also use a dose of balance. Setting goals is great. Expecting stretch goals to happen is something quite different. Thanks in part to social media, reasonable expectations are being inflated. More to the point, they are inflated either by those who know not of what they are saying or are trying to be misleading. Executives, management and employees alike

need to moderate and balance how much they believe on social media. Discerning fact from fake is becoming essential to survive in the workplace as well as in life.

In this new year, looking around at all the extremism taking place, it seems to me we need to recalibrate toward moderation, balance, reasonableness and pragmatism to truly enjoy success. **EP**

**PETER BIGELOW** is president of FTG Circuits Haverhill; (imipcb.com); pbigelow@imipcb.com. His column appears monthly.

# You have a problem, Datest has the solution.

Datest now features fast, high-energy microfocus CT services for anyone who wants to know why something broke, stopped working, won't start working, or never worked.

OK, so it's bad news, but it's news. You can work with that.

47810 Westinghouse Drive • Fremont, CA 94539 Phone: 510-490-4600 • Fax: 510-490-4111 Email: Info@datest.com • Website: www.datest.com

## 2024 a Buyers' Market for PCBs

#### Capacity is about to peak, and demand has slackened.

PRINTED CIRCUIT BOARD buyers can capitalize this year on cost-saving opportunities if they're smart about it. Here are some factors to consider:

- Compared to a year ago, fluctuations in material pricing have settled.

- Worldwide semiconductor revenue declined by 11% and overall personal computer shipments fell almost 15% last year.

- Lead-times from Asia are relatively short compared to this time last year.

- PCBs manufactured in China and then imported into the US still face a 25% tariff. But the tariff exemption on two and four-layer rigid boards has been extended through the end of May 2024.

- Speaking of tariffs on boards made in China (as well as "Out of China" policies being adopted by some customers), new board houses are being built in India, Thailand, Vietnam and Malaysia to help offset those tariff costs and offer purchasers the option to buy elsewhere.

- Many companies in China are allowing employees to leave early to enjoy the Chinese New Year holiday because business there is down.

What does all this mean? Offshore capacity is, or very soon will be, at an all-time high, while demand is down. Pricing in these conditions becomes far more negotiable, and there are bargains to be struck.

And it's not just offshore board houses that are in the midst of a slowdown. Business at

domestic shops is not as robust, either.

This is the time to shop, PCB buyers. And the time to save.

Your company needs a solid board-buying strategy for 2024, or it will miss out on these costsaving opportunities. Does your firm have one?

Here are some helpful hints to capitalize on 2024 spending:

**Price checks.** One way to do this is an activity I call "quoting for fun." Don't hesitate to give potential vendors a shot at quoting an ongoing project "for fun." Let potential vendors know it's an existing project and you'd like to see where they stand on pricing.

Also, let *all* your vendors know you will be testing the waters and comparing their pricing to others. A vendor that is too comfortable with your business may think twice about whether they could offer a better price when sending you that next quote. Be sure you follow through on checking out other vendors' prices. And don't be reluctant to bring on new vendors, if necessary.

While a few pennies per board difference in price is not worth switching vendors if you're happy with existing ones, it's wise to always keep your options open. This practice will also help keep your vendor base on its collective toes.

If you are happy with the delivery and quality of your vendor, that's great. Checking prices will still provide a useful benchmark. And if there *is* a significant per-board price difference, you can use your cost comparison as a negotiation tactic with the present vendor. Say something like: "Why is (XYZ company) 16% less than you, with all other things being equal? We are under pressure to reduce costs, and we are not necessarily asking you to meet or beat what was quoted. But how can we get closer?"

And just like that, you are likely to get a better price from a known quality vendor.

**Vendor visits.** Demand your vendors pay a visit to your operation. The more business they do with you, the more visits should be required. I can't tell you how much this helps in the

ongoing negotiation process. The more excited the vendor is about your operation, the better the service and pricing will be. If a vendor doesn't visit, this means they are too comfortable with your business, or they really don't want it. That may well mean you're paying too much.

**Keep a scorecard.** How often do you review the performance of your vendors? A vendor that is regularly evaluated for on-time delivery and quality acceptance in comparison to its competitors will generally also offer better pricing. Also, it is important that the pricing being compared is evaluated between like vendors. For example, pricing from one domestic PCB shop can be measured against another domestic house, and offshore pricing compared to another offshore manufacturer.

**Pay on time.** The one thing the vendor should never have to worry about is on-time payment. Consistent payment to vendors makes it easier for you to demand better service and pricing. There shouldn't be any excuse for a vendor to not jump through hoops for you.

I understand everyone is busy these days. But that ingrained habit of not looking outside the present cozy and comfortable PCB box is keeping many companies from saving money on bare boards, one of the most expensive items found on the bill of materials.

It's a core buyer responsibility to keep vendors competitive in pricing, and it is management's job to ensure buyers are not so overwhelmed with other responsibilities that they neglect that core duty.

This is a great time to look closely at what you're spending on PCBs and take advantage of the savings available in 2024.

**GREG PAPANDREW** has more than 25 years' experience selling PCBs directly for various fabricators and as founder of a leading distributor. He is cofounder of DirectPCB (directpcb.com) and can be reached at greg@directpcb.com.

### Move Beyond the Fixture – ....To Greater Flexibility and Cost Savings with TAKAYA!

Eliminate slow, costly test fixturing for PCBAs with the automated flexibility of TAKAYA Flying Probe testing.

- It's the best choice for high-mix assembly. No high costs and needless delays. ECOs?

- No problem no new fixture is needed, just a simple programming change.

Plus, TAKAYA has the full path to complete flying probe test automation with 4.0 level line integration, communications, and nearzero operator assistance.

- Ultimate Flexibility for High Mix, Medium Volume Assembly

- No High-Cost Fixturing

- Fast ROI

- Single or Double-sided PCBAs

- Shipped from/serviced in the U.S. by TEXMAC USA.

Find out more. Visit www.texmac.com/takaya today.

## **Understanding Your Customers**

#### A one-size-fits-all approach can lead clients to your competition.

RECENTLY I HAD an under-the-slab plumbing leak. I've been using a plumber who has deliberately kept his business small for over three decades. He is responsive, but complex jobs often take longer because he doesn't have all the tools the larger plumbing firms carry in their vans. He also doesn't have their overhead, so for most jobs he is more cost competitive. I called and he walked me through shutting off the water at the meter because he couldn't come until the next day. Part of my childhood was spent in Florida, so I applied my post-hurricane water management skills while I was without running water.

Sadly, when he arrived, he was unable to determine the source of the leak. Watching the meter spin, he mentioned it was a big one. He recommended a water leak detection firm. Its voice mailbox was full, however, and said it sometimes took a couple of days for them to return calls. My plumber reassured me he would come back after we found the leak. I got on the computer and found a water leak detection firm that operated 24/7. Fifteen minutes later they were at my house and 30 minutes after that we knew where the leak was. They were able to cut a hole in the wall and cut off the bad pipe so I could have water in the rest of the house. They couldn't fix the leak until the next day, and it would likely involve more demolition to reroute the pipe, so I had a decision to make.

Did I want to go with my reliable plumber who didn't have the same time-sensitivity or power tools as the team specializing in plumbing leaks, or did I want to pay the larger firm roughly double what my plumber would likely charge? I opted for the faster, more expensive operation. It was a good choice because they had to remove a tile I couldn't replace and cut through an exterior brick wall to do the repair. Their tools did the job in a way that was easy to repair, and they installed an access panel in the brick wall, plus closed up all the wall and tub surround holes before they left. My regular plumber would have gotten the pipe reroute done, but the demolition and subsequent repair would not have been nearly as elegant.

I often draw parallels between electronics manufacturing services (EMS) providers and some of my business transactions, and this example has a clear EMS parallel. Many OEMs choose job shops or regional manufacturers for the convenience they represent and their ability to handle projects that don't fit well in larger EMS companies. Their lower overheads often translate to lower pricing, and the industry has evolved to a point where there isn't much difference in core capabilities among different tiers. In most cases, choosing a job shop or a regional EMS provider for product volumes that don't run well in a larger EMS provider is the best business decision. That said, when a smaller EMS company loses a customer, it is often over reasons like this plumbing example. Something was keeping the customer up at night that changed the dynamics of the relationship, and the EMS provider didn't recognize that the problem required a different approach. Or the way a project challenge was handled convinced the customer that more complex projects should go elsewhere.

Two lessons are to be learned from this. First, smaller EMS providers must be sensitive to customers' sense of urgency because ignoring an urgent issue can open the door to comparison with competitors with a broader range of services and a dual-sourcing strategy. Defining the response based on the criticality of the problem rather than taking a one-size-fits-all approach can help minimize this risk. Just as you would do an FMEA on product design, consider doing FMEA on key customer relationships. What situations should drive a different approach? How will you resource that? Having this game plan in place is particularly important when the issue involves a new project that could be sourced elsewhere.

The second lesson is for OEMs. Most relationships with smaller EMS providers have a convenience factor. There can be more flexibility, faster fixes on short notice and usually better prices for projects that have a lot of changeovers. If an unusual situation isn't handled well by a long-term source that has been reliable most of the time, switching suppliers may not be the best decision. A candid conversation about why a specific issue needs to be handled differently may be a better solution. If lack of responsiveness has been a trend driven by lack of resources, however, reevaluation of sourcing options may be the best choice.