**Burkhert: Copper Thickness Considerations**

pcdandf.com hcuitsassembly.com September 2024 DESIGN & FAB CREUT

# HIGH-VOLTAGE RELIABILITY

Do Industry Standards Stack Up to Real-Life Conditions?

High-Speed **Signal Integrity** Water Quality in **Aqueous Cleaning** Diagnosing **Solder Mask** Issues This issue of PRINTED CIRCUIT DESIGN & FAB/CIRCUITS ASSEMBLY is brought to you by:

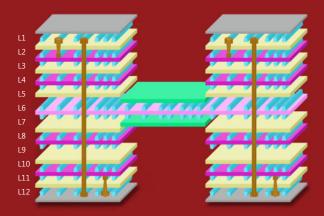

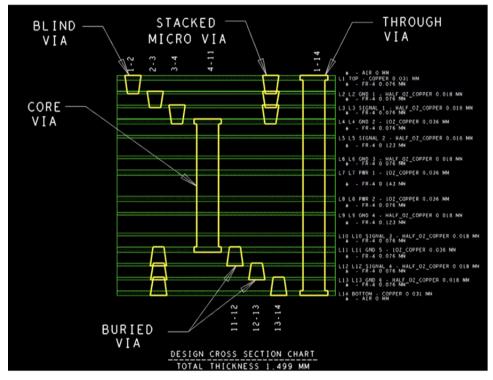

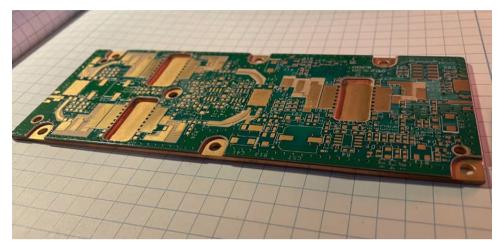

# Leaders in HDI Manufacturing

12-Layer Rigid HDI, 370HR, 0.040" Thick, Stacked via 3+N+3, Blind via L1-L2, L1-L4, L4-L9, L9-L12 & L11-L12 Non Conductive via Fill, 0.004" hole, 0.003" Trace/Space, Controlled Impedance

If you require any assistance with HDI PCB design and assembly,

our engineers are ready to help you.

# Get a free quote

PCB TRACE 20 YEARS OF MANUFACTURING EXPERIENCE WITH BLIND AND BURIED VIAS, RIGID FLEX & FLEX PCB

RUSHPCB

20 YEARS OF MANUFACTURING EXPERIENCE WITH BLIND AND BURIED VIAS, RIGID FLEX & FLEX PCB ELECTRONIC DESIGN, & QUICK TURN CIRCUIT BOARDS, ASSEMBLY & FULL TURNKEY

# Multilayer PCB Stackup

12 Layer Flex Rigid, 0.030" Thick Rigid, 0.008" Thick Flex Blind Via L1-L2 & L11-L12, 0.003" Hole, Resin Filled, 0.002"/0.002" Trace/Space, Controlled Impedance

Manufactured on August 2016

# When you're in a rush call RUSH PCB

Affordable Pricing \* Satisfaction Guarantee \* Fast Response \* Free Quote \* Fast Shipping HDI Boards \* Stacked Micro Vias \* 2 mil line & Space \* Flex & Rigid Flex

# Located in the Silicon Valley PCB up to 12 Layers in 3 days PCB Assembly Same Day Turn Full Turnkey Service

Certified: ISO9001/ITAR/UL

www.rushpcb.com | Sales@rushpcb.com | 1 408 496 6013 Rush PCB Inc, 2149-20 O'Toole Ave, San Jose, CA 95131, U.S.A

See us at PCB West Booth #306

# Measure PCB Surface Finishes ENIG, EPIG, EPAG & ENEPIG

Xray

- XRF with Automated X-Y Table

- Increased Throughput

- Improved Reliability

- IPC 4552 B & IPC 4556

Measuring Made Easy®

www.fischer-technology.com | info@fischer-technology.com | 860.683.0781

#### FIRST PERSON

THE ROUTE Preparing for UHDI. Mike Buetow

#### MONEY MATTERS

ROI A new level of miniaturization. Peter Bigelow

BOARD BUYING The next PCB powerhouse? Clement Yuen

FOCUS ON BUSINESS Put a stop to self-idolization. Jake Kulp

#### TECH TALK

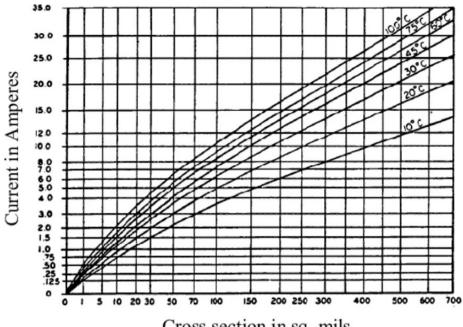

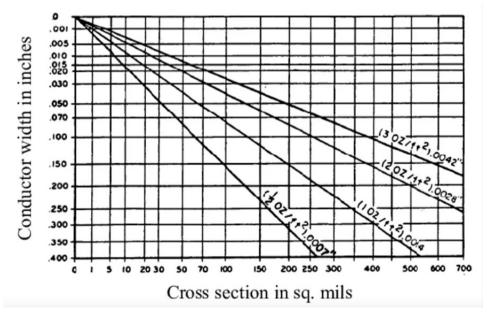

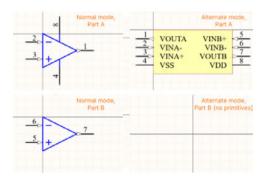

**DESIGNER'S NOTEBOOK** Pay attention to copper thickness. John Burkhert Jr.

MATERIAL GAINS New materials for 6G and beyond. Alun Morgan

ROUGHLY SPEAKING Expanding your knowledge. Geoffrey Hazelett

SEEING IS BELIEVING Withstanding the tide of offers. Robert Boguski

GETTING LEAN Al and continuous improvement. Filemon Sagrero

#### **TECHNICAL ABSTRACTS**

#### DEPARTMENTS

**AROUND THE WORLD**

PCEA CURRENT EVENTS

**MARKET WATCH**

**OFF THE SHELF**

# PRINTED CIRCUIT DESIGN & FAB CIRCUITS ASSEMBLY

#### FEATURES

#### **HIGH-SPEED DESIGN**

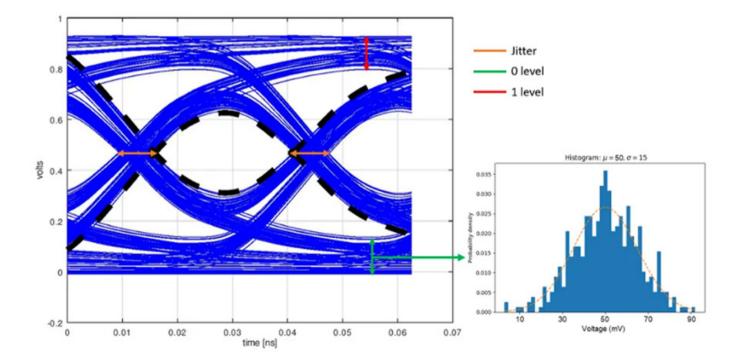

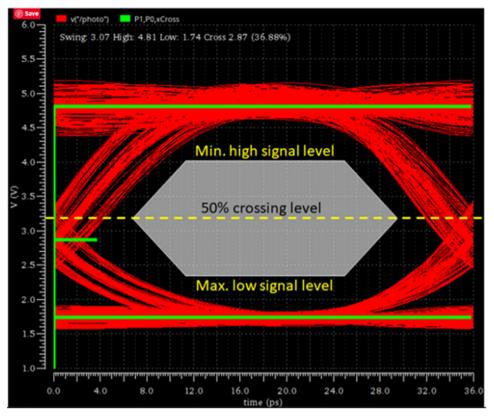

#### **Fundamentals of Signal Integrity at Various Frequencies**

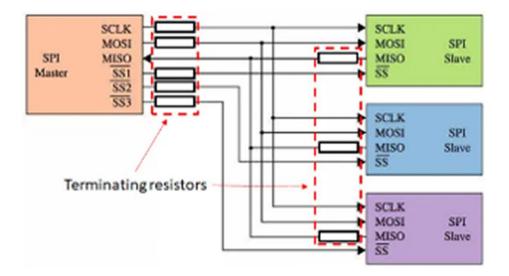

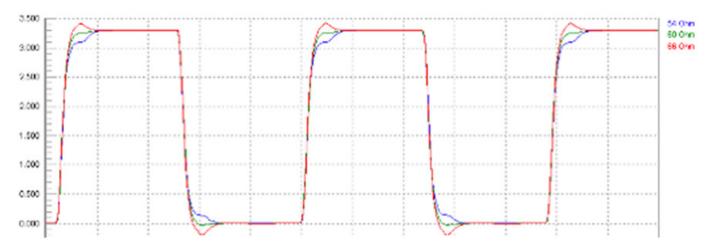

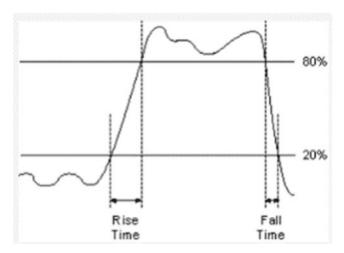

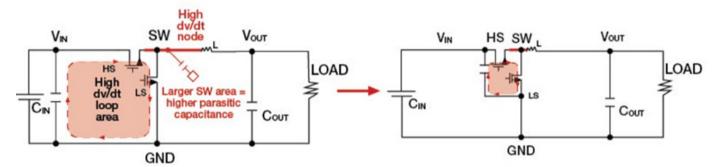

PCB designers use CAD tools or the internet to find best practice techniques for designing at different frequencies, but they may not understand the fundamentals behind signal integrity or miss lesser-known techniques. An exploration of board-level tips and a discussion of fundamentals from lower-speed designs to gigabit-level speeds.

by ANDREW GONZALES and JASON METZNER

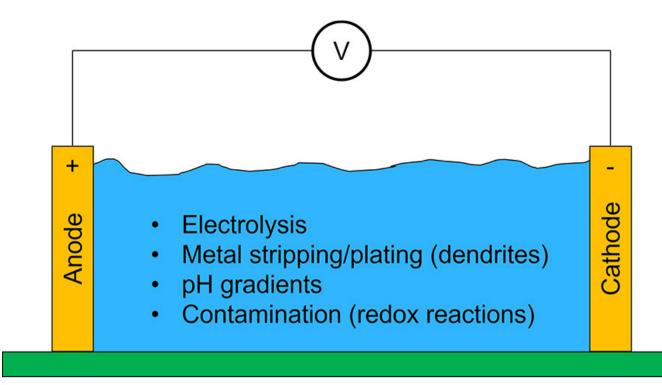

#### SIR TESTING (COVER STORY)

#### **Dendrite Growth Dynamics**

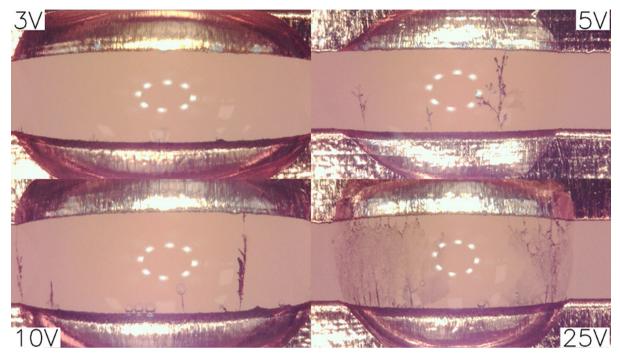

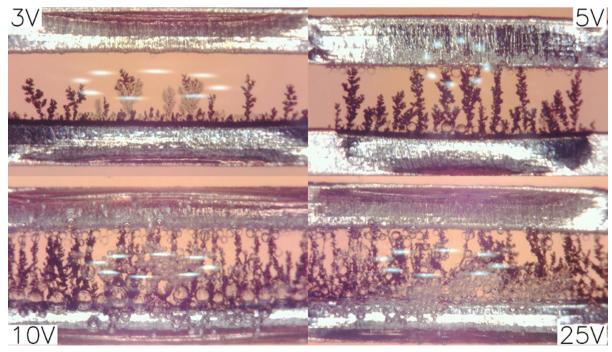

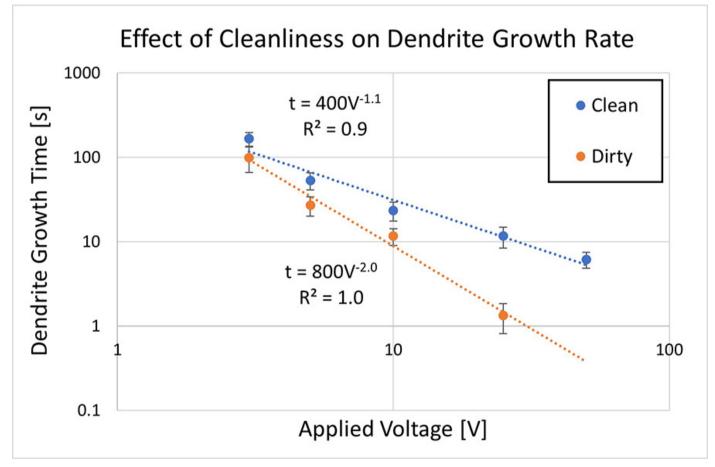

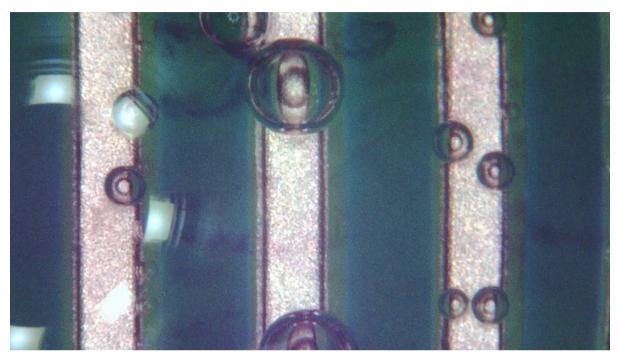

With the growing prevalence of high-voltage electronics seeing daily use by consumers, the reliability of those electronics is increasingly important – including the question of whether they should be tested at those elevated voltages or whether the conventional 5V SIR test is adequate. To answer that question, a series of tests was conducted to understand how higher voltages and contamination affect dendrite growth on a SIR test coupon.

by ADAM KLETT, PH.D.

#### **AQUEOUS CLEANING**

#### Water Quality Matters

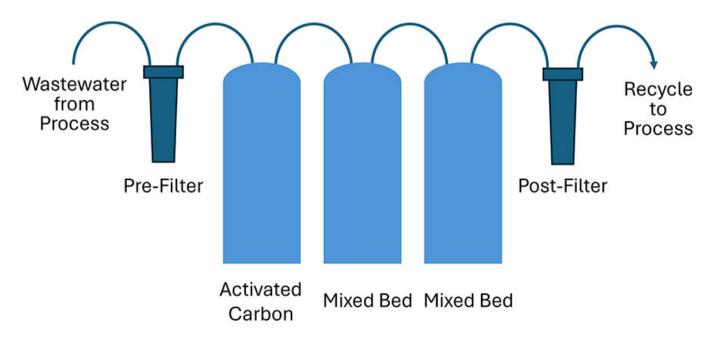

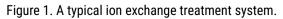

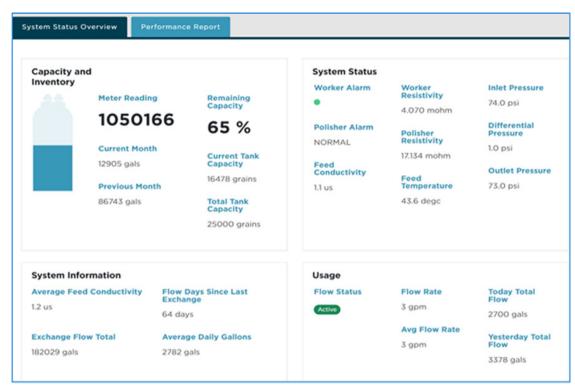

Aqueous cleaning in PCB assembly requires particular attention to water quality to minimize the risks of contamination of the board, with ion exchange being the technology of choice to purify and recover the water. Ion exchange systems typically require manual monitoring or timed changing of water tanks to maintain quality, and a case study is presented using an ion exchange system with remote monitoring capabilities to reduce water usage and minimize manual monitoring. by CHRISTOPHER T. RILEY

#### **BOARD QUALIFICATION**

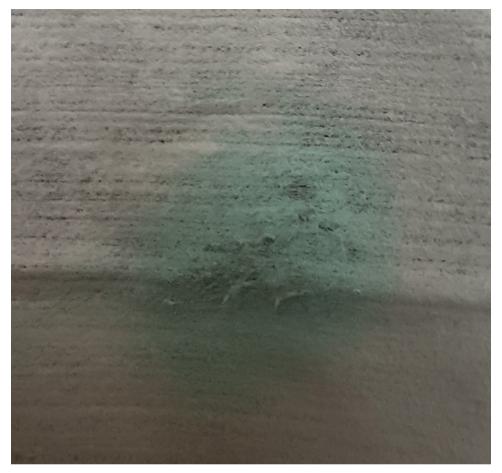

#### Identifying Solder Mask Problems with Simple Tests

Solder masks can face several issues that can lead to complications like micro solder balling, bridging and solder snail trails, which could compromise PCB quality and long-term reliability. To prevent significant production rework and increased costs, a few simple tests are presented that an engineer can perform on the shop floor.

by TIMOTHY O'NEILL

## ON PCB CHAT (PCBCHAT.COM)

#### SMTA INTERNATIONAL PREVIEW with JASON KEEPING, JEFF KENNEDY

and ROBERT BOGUSKI

#### SUPPLY CHAIN MANAGEMENT with 7ACHARY FEUERSTEIN

PCB Chat

AOI AND X-RAY BEST PRACTICES with JOEL SCUTCHFIELD and JESPER LYKKE

**OPTIMIZING PCB DESIGN** with DUNCAN HALDANE

# Support For Flex, Rigid Flex and Embedded Component Designs Now Available.

DownStream's CAM350 and BluePrint-PCB support importation and visualization of PCB designs containing Flex, Rigid Flex or Embedded components. Visualize designs in both 2D and 3D, and easily document complex Flex or Rigid- Flex Stack-Ups for submission to PCB Fabricators.

- Import and Visualize Flex, Rigid-Flex and Embedded Component Designs

- 3D Visualization to Validate PCB Construction and Component Assembly

- Manage Variable Stackup Zones for Rigid-Flex Designs

- Easily Create Custom Flex or Rigid-Flex Fabrication and Assembly Documentation

- Use DFM analysis to analyze a flex or rigid-flex design for potential fabrication or bend related defects

Use Stack Up Visualizer and Blueprint's Rigid-Flex Stackup template to easily manage and document rigid-flex stackups.

Use Rigid-Flex and Inter-layer DFM analysis to analyze flex and rigid-flex designs.

For more information visit downstreamtech.com or call (508) 970-0670

PCEA PO BOX 807 AMESBURY, MA 01913

#### PCEA BOARD OF DIRECTORS

Stephen Chavez, CHAIRMAN Justin Fleming, SECRETARY Gary Ferrari, CHAIRMAN EMERITUS

#### MEMBERS

Jim Barnes Michael Buetow Tomas Chester Douglas Dixon Richard Hartley Matthew Leary Scott McCurdy Anaya Vardya Susy Webb Eriko Yamato

#### PCEA.NET

#### THE PRINTED CIRCUIT ENGINEERING ASSOCIATION, INC. BRANDS:

| PUBLICATION                |                              |

|----------------------------|------------------------------|

| PCD&F/Circuits Assembly    | digital.pcea.net             |

| WEBSITES                   |                              |

| PCD&F                      | pcdandf.com                  |

| Circuits Assembly          | circuitsassembly.com         |

| NEWSLETTER                 |                              |

| PCB Update                 | pcbupdate.com                |

| PODCASTS                   |                              |

| PCB Chat                   | pcbchat.com                  |

| EVENTS                     |                              |

| PCB West                   | pcbwest.com                  |

| PCB East                   | pcbeast.com                  |

| EDUCATION                  |                              |

| PCB2Day                    | pcb2day.com                  |

| PCEA Training              | pceatraining.net             |

| Printed Circuit University | printedcircuituniversity.com |

| AWARDS PROGRAMS            |                              |

| Service Excellence Awards  | circuitsassembly.com         |

| NPI Awards                 | circuitsassembly.com         |

|                            | pcdandf.com                  |

| DATABASE                   |                              |

| Directory of EMS Companies | circuitsassembly.com         |

#### MANAGEMENT

PRESIDENT

Mike Buetow 617-327-4702 | mike@pcea.net VICE PRESIDENT, SALES & MARKETING

Frances Stewart 770-361-7826 | frances@pcea.net

#### PCD&F/CIRCUITS ASSEMBLY EDITORIAL

MANAGING EDITOR

Tyler Hanes 205-258-0067 | tyler@pcea.net

#### **COLUMNISTS AND ADVISORS**

Peter Bigelow, Robert Boguski, John D. Borneman, John Burkhert, Jr., Stephen Chavez, Geoffrey Hazelett, Mark Finstad, Nick Koop, Jake Kulp, Alun Morgan, Susan Mucha, Greg Papandrew, Chrys Shea, Jan Vardaman, Gene Weiner

#### PRODUCTION

```

ART DIRECTOR & PRODUCTION

blueprint4MARKETING, Inc. | production@pcea.net

Nathan Hoeller | nathan@pcea.net

```

#### SALES

VICE PRESIDENT, SALES & MARKETING Frances Stewart 770-361-7826 | frances@pcea.net SENIOR SALES EXECUTIVE Will Bruwer 404-313-1539 | will@pcea.net

#### REPRINTS

sales@pcea.net

#### **EVENTS/TRADE SHOWS**

EXHIBIT SALES Frances Stewart 770-361-7826 | frances@pcea.net TECHNICAL CONFERENCE Mike Buetow 617-327-4702 | mike@pcea.net EVENTS MANAGEMENT Jacqueline Bress 404-955-7675 | jacqueline@pcea.net

#### SUBSCRIPTIONS

PRINTED CIRCUIT DESIGN & FAB/CIRCUITS ASSEMBLY is distributed without charge to qualified subscribers. To subscribe, visit pcdandf.com or circuitsassembly. com and click on Subscribe. For changes or cancellations to existing subscriptions: subscriptions@pcea.net

PRINTED CIRCUIT DESIGN & FAB/CIRCUITS ASSEMBLY is published monthly by Printed Circuit Engineering Association, Inc., PO Box 807 Amesbury, MA 01913. ISSN 1939-5442. GST 124513185/ Agreement #1419617.

© 2024, Printed Circuit Engineering Association, Inc. All rights reserved. Reproduction of material appearing in **PRINTED CIRCUIT DESIGN & FAB**/ **CIRCUITS ASSEMBLY** is forbidden without written permission.

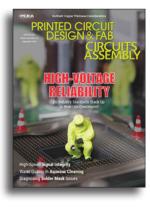

# Move Beyond the Fixture – ....To Greater Flexibility and Cost Savings with TAKAYA!

Eliminate slow, costly test fixturing for PCBAs with the automated flexibility of TAKAYA Flying Probe testing.

- It's the best choice for high-mix assembly. No high costs and needless delays. ECOs?

- No problem no new fixture is needed, just a simple programming change.

Plus, TAKAYA has the full path to complete flying probe test automation with 4.0 level line integration, communications, and nearzero operator assistance.

- Ultimate Flexibility for High Mix, Medium Volume Assembly

- No High-Cost Fixturing

- Fast ROI

- Single or Double-sided PCBAs

- Shipped from/serviced in the U.S. by TEXMAC USA.

Find out more. Visit www.texmac.com/takaya today.

# Let's Get Small

ULTRA-HIGH-DENSITY INTERCONNECTS ARE more smoke than fire right now, but they won't be that way for long. Driven by high-density BGAs and RF products, UHDI is finding its way into the mainstream.

Given the number of conferences, webinars and the like, readers would be forgiven if they thought UHDI was already standard, however.

First, of course, means agreeing on what, exactly, UHDI is. The working definition of UHDI is product with line widths and spaces of fewer than 50 microns, dielectric thickness of less than 50 microns, and a microvia diameter of less than 75 microns. That's not a standard definition – yet – and the lower lever parameters have yet to be defined. At some point, there stands to be overlap with semiconductor technology. Stay tuned as the definition evolves.

I am reminded – to a degree – of the chaos surrounding UHDI's (slightly) larger cousin, high-density interconnects, which hit widespread production in the late 1990s (although the original concept dates much earlier). Then, the issues could be boiled down to two:

- Which process to use: etch or drill (and if drill, mechanical or laser)?

- The demand signal.

As to the former, some of the processes of the day included photovia, plasma etching and the eventual winner, laser. As to the latter, time will tell as to the ultimate market size, but orders are already coming.

It's mostly lost to history now, but not every company banked on laser at the start. Motorola, for instance, produced millions of boards using a sequential build HDI process that mated photoimageable dielectrics and semiadditive copper metallization on a PWB substrate.

And even fewer companies – or regions, really – saw the need. North America and Europe were all about big boards in those days. Japan controlled IC substrate production. Taiwan and especially China were still relatively marginal players. Still, the signs were ominous. Key industry observers were already piping up that investment in microvia formation, specifically in laser drills, was needed.

The West wasn't listening. Indeed, upon seeing the buoyant forecasts for the PCB industry in North America for the early 2000s, I recall Jack Fisher, then the CTO of the Interconnection Technology Research Institute, remarking that it would be years before Americans started pursuing HDI. How right he turned out to be. And when the major telecommunications and IT companies started canceling orders en masse for their so-called "surfboards," the Western PCB shops weren't left with much to fall back on.

Asia, on the other hand, led by Taiwan and Japan, invested heavily on leading-edge drilling capacity. Today, we all know the Pacific Rim dominates high-end PCB fabrication.

Could the script be flipped? Unlike with HDI, additive fabrication processes look like they will have a significant role in UHDI. It's unlikely a single solution will dominate.

We have a long way to go to mainstream this technology. IPC task groups are working on various specifications for fabrication and qualification, among others. Designers need to understand component choices, signal integrity implications, impedance matching, and thermal management. Assemblers will have to master the use of smaller powder sizes, different stencils, and so forth.

According to John Johnson at American Standard Circuits, one of the handful of PCB fabricators in the US capable of UHDI production, when lines and spaces reach less than 25 microns, UHDI is needed. To be sure, that's really small. But while conventional technology will continue to have a long runway, those who master UHDI will be betterpositioned to take advantage of the smaller, thinner, lighter products consumers of all stripes demand.

A special free panel on UHDI at PCB West this year will outline the basic various ways UHDI processing takes place, and to help designers and design engineers understand how their decisions might affect yield. Among the panelists are Michael Gleason of GreenSource Fabrication; Meredith Labeau of Calumet Electronics, Anaya Vardya of American Standard Circuits/Sunstone, and Jay Vyas of SigmaTron International.

The panel takes place at the Santa Clara Convention Center on Oct. 9 from 9-10 a.m. We invite all our readers to join us for this and several other free sessions that day, and to take in the more than 100 leading electronics design, fabrication and assembly companies on hand during the one-day exhibition.

See you at the show!

mike@pcea.net @mikebuetow

P.S. The video from our forum on UHDI & Substrates: From Design to Package will be available at PCEA.net later this month. Also, a series of videos on printed circuit board design will be available on our YouTube channel.

MIKE BUETOW is president of PCEA (pcea.net); mike@pcea.net.

# TURNING IDEAS INTO REALITY

PCBWAY EMPOWERS INNOVATORS WORLDWIDE

Join the **PCBWay revolution** today and turn your **imagination** into **reality!**

# WWW.PCBWAY.COM

SERVICE@PCBWAY.COM

# ENGINEERED TO PERFECTION

Our state-of-the-art facilities and expert team of engineers ensure that your designs are brought to life with the utmost precision and efficiency, from a small-scale prototype to a large-scale production run.

> See us at PCB West Booth #616

QUALITY ASSURANCE

Illustrate PCBWay's rigorous quality control processes, emphasizing that every product undergoes meticulous testing to ensure it meets the highest industry standards.

# GLOBAL REACH

Highlight PCBWay's extensive network, reaching innovators across the globe. Mention our fast and reliable international shipping options.

# CUSTOMER SUPPORT

Emphasize PCBWay's commitment to outstanding customer service, featuring a dedicated team of experts available 24/7 to assist with any inquiries or support needs.

# Jedec Releases Plans for Memory Module Standards

**NFWS**

ARLINGTON, VA – Jedec has announced upcoming standards for advanced memory modules designed to power the next generation of high-performance computing and AI applications.

The standards for DDR5 multiplexed rank dual inline memory modules (MRDIMM) and a next-generation compression-attached memory module (CAMM) for LPDDR6 are set to change the industry with unparalleled bandwidth and memory capacity.

DDR5 MRDIMMs offer an innovative, efficient new module design to enhance data transfer rates and overall system performance. Multiplexing permits multiple data signals to be combined and transmitted over a single channel, effectively increasing bandwidth without the need for additional physical connections and providing a seamless bandwidth upgrade to enable applications to exceed DDR5 RDIMM data rates. Other planned features include:

- Platform compatibility with RDIMM for flexible end-user bandwidth configuration

- Utilization of standard DDR5 DIMM components including DRAM, DIMM Form Factor & Pinout, SPD, PMIC, and TS for ease of adoption

- Efficient I/O scaling using RCD/DB logic process capability

- Leverage existing LRDIMM ecosystem for design and test infrastructure

- Support for multi-generational scaling to DDR5-EOL.

The Jedec MRDIMM standard is set to deliver up to twice the peak bandwidth of native DRAM, enabling applications to surpass current data rates and achieve new levels of performance. It maintains the same capacity, reliability, availability, serviceability (RAS) features as Jedec RDIMM. The committee aims to double the bandwidth to 12.8Gbps and increase the pin speed. MRDIMM is envisioned to support more than two ranks and is being designed to utilize standard DDR5 DIMM components ensuring compatibility with conventional RDIMM systems.

Plans are underway for a tall MRDIMM form factor to offer higher bandwidth and capacity without changes to the DRAM package. This taller form factor will enable twice the number of DRAM single-die packages to be mounted on the DIMM without the need for 3DS packaging.

As a follow-on to Jedec's JESD318 CAMM2 memory module standard, JC-45 is developing a next-generation CAMM module for LPDDR6 targeting a maximum speed greater than 14.4 GT/s. As planned, the module will also offer a 24-bit subchannel, a 48-bit channel and a connector array.

Both projects are in development in Jedec's JC-45 Committee for DRAM Modules. Jedec standards are subject to change during and after the development process. **P**

# Renesas Completes \$5.9B Altium Acquisition

TOKYO – Renesas in August announced the successful completion of its \$5.9 billion acquisition of Altium, which was first announced in February.

The combination sets the foundation for Renesas and Altium to create a common electronics system design and lifecycle management platform, Renesas said in a release. The platform will integrate and standardize various electronics design data and functions and enhance component lifecycle management, delivered in digital iterations.

"This is a historical milestone for both Renesas and Altium as we take another important step forward in bringing enhanced user experience for electronics system designers," said Hidetoshi Shibata, CEO, Renesas. "The integrated and open electronics system design and lifecycle management platform we aim to build together will make electronics accessible to broader market, for any enterprises regardless of their size or industry. I want to reaffirm that our commitment to upholding data security and compliance of the Altium customers will continue to be our top priority."

With the transaction now closed, Altium is now a wholly owned subsidiary of Renesas. Altium CEO Aram Mirkazemi has assumed the role of senior vice president and head of Renesas' Software & Digitalization. He concurrently serves as CEO of Altium.

"This is a pivotal moment for Altium and marks the beginning of an exciting future with Renesas," Mirkazemi said. "With Renesas' support and expertise, we are looking forward to accelerating the cloud-enablement of all industry processes associated with electronics design and development. This will make electronics accessible to a broader market and lay the foundation for software-defined products." **P**

# SIA Report Provides Recommendations for Domestic Semiconductor Growth

WASHINGTON – A new report from SIA and the Boston Consulting Group identifies five primary factors that impact investment decisions for semiconductor companies. "Attracting Chips Investment: Industry Recommendations for Policymakers" also lays out actionable recommendations for governments seeking to grow their domestic semiconductor industry.

#### Among the factors:

1. Investment and operational costs. Semiconductor development, in both design and manufacturing, is expensive. In evaluating site options, companies thoroughly analyze site-specific costs, including land, utilities, equipment, materials, labor, and taxes. Government support programs that are simple, flexible, and offset

construction and equipment costs are attractive to semiconductor investors.

- 2. Semiconductor companies require access to a large technical workforce. They seek countries where the education system and public-private partnerships coalesce to generate a rich talent pipeline—from technicians and skilled trades to Ph.D-level engineers and scientists. Governments that adopt comprehensive workforce development and labor policies to build an industry-ready talent pipeline will be well-placed to draw investment from the semiconductor industry and other strategic technology sectors.

- 3. Safe, reliable, and cost-efficient water, utilities, communications, and transportation infrastructure are critical for semiconductor operations. Small interruptions in operations can incur significant costs. Governments should invest in electricity grids that are able to maintain day-to-day stability, provide a portion of energy from green sources, and ensure communications and transportation networks are sufficient to support semiconductor industry needs.

- 4. Regulatory and trade environment. Semiconductor supply chains are concentrated in countries with marketfriendly trade policies, and regulatory frameworks that respect intellectual property rights and trade compliance. Policymakers can facilitate semiconductor investments by implementing policies that minimize trade and permitting costs, streamline administrative processes, and facilitate the movement of semiconductor products and data.

- 5. Integrated ecosystems. Semiconductor companies thrive on vibrant ecosystems that cluster suppliers, customers, R&D partners, educational partners, and innovative talent.

Governments seeking to present their countries as a destination for semiconductor companies to invest must move quickly and deliberately to take advantage of this window of opportunity, mindful that other governments are competing for such investments, the report says.

The policy recommendations, if followed, can position countries to attract chip ecosystem investments that complement industry operations in the United States, and drive greater security, resilience, and diversification in global semiconductor supply chains, the report concludes.

# Long Young to Build 2 Thai Factories

KUNSHAN, CHINA – Long Young Electronic has announced plans to invest CNY200 million (\$28 million) to build two new factories in Thailand.

The Chinese supplier of electromagnetic interference shielding materials said it will spend up to CNY120 million (\$16.8 million) on a composite copper foil plant and CNY80 million (\$11.2 million) on an EMI shielding materials plant in Thailand's northern Chachoengsao province.

The company said the composite copper foil plant will take four years to construct and is designed to produce various types of products, targeting printed circuit board makers in Southeast Asia and other markets. The other factory will be built in three years with a production capacity of 62,400 sq. m. of conductive tape and 352 million EMI shielding and related materials a year.

To pay for the new facilities, Long Young said it will terminate a plan to build a new EMI shielding material plant and expand the capacity of an existing one in China and will suspend construction of a product research and development center.

# Benchmark Expands Romanian Facility

TEMPE, AZ – Benchmark Electronics has opened an expansion at its Brasov, Romania, facility that more than doubles its manufacturing capacity in the region.

The EMS company said the expansion is intended to support customer-driven demand for access to high-technology manufacturing solutions, localized and global supply chains, and a customer-focused team committed to optimizing delivery, quality, cost, and manufacturing and engineering services. Key market sectors serviced include complex industrials, medical and semiconductor capital equipment.

"Benchmark Brasov, alongside Benchmark Almelo, serves as the heart and soul of our European operations and we are excited to expand our manufacturing footprint, add capacity to better serve our current customers, and support the high interest by new customers who are looking to regionalize their manufacturing in Europe," said Jeff Benck, president and CEO, Benchmark. "The new space will offer our manufacturing and engineering teams ample room to expand our operations in eastern Europe while also bringing more high-paying jobs to the Brasov community."

The expansion of Brasov is part of a broader company strategy to increase manufacturing capacity around the world by leveraging its current facilities and leadership as more customers look to diversify their manufacturing strategy and have products built closer to end-market consumption, the company said, and the new space not only provides new manufacturing space, but also improves system integration and workflow on the floor.

"It is an honor to welcome our partners, suppliers and the local community for the unveiling of our expanded Brasov facility," said Herman Bartelink, vice president of European operations, Benchmark. "We're looking forward to adding new capabilities and bringing more business and jobs to the region. This expansion has been a long time coming and I am very proud of the work of our European team in reaching this milestone." **P**

# Kimball Sells AT&M Unit to Averna

JASPER, IN – Kimball Electronics has completed the sale of its automation, test and measurement business to Averna, and said it plans to focus on its core EMS business.

The sale to Averna Technologies closed on Jul. 31, with proceeds from the transaction being used for support of organic growth, debt reduction and share repurchases, Kimball said in a release. Financial terms of the sale were not disclosed.

Kimball entered the automation, test, and measurement industry with the acquisition of Global Equipment Services in 2018, and in May 2024 announced that the unit was for sale. The AT&M business provides advanced testing and

inspection solutions for manufacturers in the industrial, medical, consumer electronics, and semiconductor sectors.

"While we have made significant strides enhancing our capabilities in AT since the acquisition of GES, we determined that it is not a good strategic fit for Kimball and that focusing on core EMS operations aligns best with strategic priorities and longer-term growth opportunities for the company," said CEO Richard Phillips. "AT will be wellpositioned under new ownership with expertise in testing and measurement, broad industry knowledge, and established client relationships. We thank the team for their contributions and wish them success moving forward."

"The addition of the GES team, and its footprint in Silicon Valley and Asia, is a perfect fit for Averna," said Francois Rainville, CEO, Averna. "This will further strengthen our position as one of the worldwide leaders focused in automation, test and measurement. Now with 1,200 professionals spanning across the Americas, Europe and Asia, we can better partner with our global customers in all aspects of their product test requirements, wherever they are. We welcome our new teammates and are looking forward to this new chapter in Averna's story." **«**P

# Meiko to Open Vietnam PCB Factory in 2025, Partners with Aoshikang

AYASE, JAPAN – Meiko Electronics is planning to begin production at its \$100 million PCB factory in Vietnam in the second quarter of 2025.

According to project's latest report, the company aims to finish construction of the factory by the third quarter of this year, install equipment during the end of the year and early 2025, recruit and train staff during the first quarter and enter official operation in the second quarter.

When finished, the factory will have an annual production capacity of 80,000 sq. m. The company also plans to build a second factory on the site, upping its total investment to \$500 million. The factories will produce PCBs for peripheral devices, computers, electronic home appliances, audio-visual equipment, solar cells, microprocessor chips and controllers.

Meiko also announced a strategic business alliance with Aoshikang Technology to boost PCB production capacity in the ASEAN region.

Through the partnership, Meiko will invest \$20 million for a 14.9% stake in ASK's subsidiary, Jiaruian, to manage a new production subsidiary in Thailand. Meiko said the collaboration aims to meet increasing demand and will have a negligible impact on its current fiscal year business results.

# Bain Capital to Acquire Italian PCB Maker Somacis

LONDON – Private investment firm Bain Capital has announced the acquisition of a controlling stake in Somacis, an Italian PCB manufacturer, from Chequers Capital.

Chequers will reinvest into the company alongside the management team, led by CEO Giovanni Tridenti. Other terms of the deal were not disclosed.

Somacis was founded in 1972 and specializes in high-mix/low-volume, and mission-critical PCBs. The company serves various high-performance markets such as aerospace & defense, MedTech, and data centers/AI, among others, and operates across the full value chain, offering R&D prototyping, ramp-up and end-to-end production. The company has a global footprint composed of five facilities in Europe, North America and Asia.

"Given its strength in the market, Somacis is well-positioned to benefit from sustainable long-term reshoring tailwinds which increase the demand for PCBs manufactured in the US and EU," said Ivano Sessa, partner and cohead of European Industrials, Bain Capital. "We are pleased to back one of the leaders in its field."

"I would like to thank Chequers for their valuable partnership and outstanding work over the past years and am pleased that they will remain invested alongside our fully committed management team as we are joined by Bain Capital," said Tridenti. "We are excited for Bain Capital to bring its expertise in international development and operational capabilities to further enhance our global reach and help us fulfil our long-term ambitions, which are underpinned by a mix of organic and inorganic strategic growth initiatives, and on the strengthening of the value-add proposition to our customers."

"Over the past years, we have worked alongside the Somacis management team to strengthen the company's operations and positioning and to make strategic acquisitions," said Philippe Guérin, managing partner, Chequers Capital. "We are very pleased to reinvest alongside Bain Capital and such an excellent management team with the goal to become the number one global player in our segment."

# SEMI Publishes Recommendations on Outbound Investments

BRUSSELS – SEMI has published recommendations to advance the European semiconductor industry in response to the European Economic Security Strategy.

The European Commission has outlined the nonbinding roadmap to monitor outward investment transactions with the goal of preventing technology and knowledge leakage in four critical technology areas tied to advanced semiconductor technologies.

The SEMI Europe Recommendations on Outbound Investments outline the association's position and strongly encourage all policymakers involved to carefully consider the following key recommendations:

• Ensure that European semiconductor companies are as free as possible in their investment decisions to avoid losing their agility and relevance across global markets.

- Adopt a pragmatic risk-based approach to comprehensively assess which outbound transactions related to advanced semiconductor technologies could result in technology leakage for dual-use purposes.

- Provide further clarification on how any potential measures would affect intra-company investments and relations with non-EU subsidiaries, given the international exposure of semiconductor companies.

- Develop an approach to outbound investments that effectively contributes to greater economic security through close consultations between European institutions, member states, and all relevant industry stakeholders.

- Maximize the synergies and positive feedback effects that the semiconductor supply chain has in increasing competition, cross-border investments and transnational collaboration.

The recommendations emphasize the need for the European Commission to adopt a positive approach to economic security that recognizes the crucial role of cross-border investments for the functioning and prosperity of the European semiconductor industry, to guarantee its companies have a high level of agility and market access at the global level.

"Within our industrial ecosystem, outbound investments are regarded by the vast majority of SEMI members as essential to scale production, expand capabilities, access emerging markets, and engage in innovative partnerships," said Laith Altimime, president of SEMI Europe.

SEMI will continue to engage with relevant stakeholders to contribute to the political debate and encourage a legislative framework that can enhance economic security across industrial supply chains while preserving Europe's technological competitiveness.

# ECIA Guide Advises Approved Channel Buying

ATLANTA – An Electronics Component Industry Association (ECIA) committee in August released an advisory to use only the authorized channel to procure electronic components. With the double threat of a steep rise in bad actors with new tools to sell fake components, combined with more frequent supply chain disruptions, it is an especially critical time to be vigilant, the trade group's Global Industry Practices Committee (GIPC) said.

The GIPC Guideline, "The Risks of Buying Components Outside the Authorized Channel," is available from the trade group's website.

"These guidelines spell out the specific risks taken when going outside the safety of the authorized channel to buy electronic components," explained Don Elario, ECIA Vice President of Industry Practices. "We urge customers to seriously consider the consequences that can occur when a counterfeit component infiltrates their BOM: catastrophic failure, brand damage, liability, and so on. Our document contrasts those risks with the assurances that come from the authentic chain of custody from the component manufacturer through the authorized channel."

# Bank Exits Welsh Electronics Manufacturer After Funding Buyout

TREDEGAR, UK – The Development Bank of Wales has exited Camtronics six years after funding a management buyout of the contract electronics manufacturer.

In 2018, the Development Bank's Wales Management Succession Fund Investment Fund invested £450,000 (\$584,000) in the company to enable managing director Paul Macleur, alongside colleagues Chris Gulliford and Linda Sterry, to lead a management buyout from Photonstar, who had purchased the company in 2011.

The Development Bank also introduced non-executive director Mark Pulman to the company at the time, and since the buyout, Camtronics' turnover has doubled to £4 million (\$5.2 million).

"As we embark on the next stage of our growth, the time was right to reflect on how the support of the Development Bank has enabled us to build a strong foundation for the future," said Macleur. "We have enjoyed the benefit of having an excellent working relationship with the team who have stood by us throughout, offering guidance and significant support in addition to funding. Together with Mark, they have helped with our strategic planning and long-term value creation which means that we are now in a position to buy them out. As the sole owners of the business, we are now well-placed to move forward and continue to grow our industry-leading services."

Camtronics offers a full range of electronics manufacturing services and has 38 employees. Services include SMT assembly, AOI, through-hole assembly, box build, programming and testing.

#### BRIEFS

# PCD&F

**Altair** signed a memorandum of understanding with the **University of Nottingham** for a digital twin project within the aerospace sector and worked with **LG Electronics Vehicle Component Solutions** to create analysis solutions aimed at increasing product lifespans using Altair's HyperWorks platform.

**Bestec Group** plans to invest INR200 crore (\$24 million) in a new manufacturing unit near Bengaluru, India.

Brandner PCB, an Estonian PCB manufacturer, will shut down its operations at the end of November.

**IEEE TryEngineering** partnered with **Keysight Technologies** to develop lesson plans focused on electronics and power simulation.

**Elite Material** and **Zhen Ding** have signed a strategic cooperation agreement to collaborate research of copper-clad laminates.

**ISU Petasys** will invest KRW300 billion (\$223 million) in Daegu, Korea, to build a PCB manufacturing plant.

**Jingguo Thailand's** PCB plant will be sold to Tongye Shenghong Technology Group for about \$23 million.

OurPCB USA opened a new office in Sierra Madre, CA.

**Siemens** and **BAE Systems** announced a collaboration to accelerate digital innovation in engineering and manufacturing technologies.

**Sumitomo Electric Industries** will invest an additional \$27.4 million in two projects for manufacturing flexible circuit boards in Vietnam's capital city of Hanoi.

TTM Technologies plans to start construction this year on a plant near Syracuse, NY.

**Ultra Librarian** announced a partnership with **Footprintku AI** to enhance DfM capabilities across its CAD library.

**Yang Xuan Electronics** began construction on a \$120 million PCB plant in Vietnam with an expected opening by the end of 2025.

**Zhen Ding Technology** has been granted a patent for a covering film that includes a thermal conductive layer sandwiched between a covering layer and an adhesive layer.

# CA

Anda Technologies appointed Tech Gear Ltd. distributor in Hungary.

Ascentron installed Ersa i-CON 1 MK2 hand soldering equipment.

Avalon Technologies announced the expansion of its PCB assembly and design services.

Axiom partnered with Switchee to create a platform of interconnected devices for social housing.

**BTU International** named **Repstronics** representative in Mexico and Central America.

Cofidur in August announced the acquisition of fellow French EMS Seico.

**Dixon Technologies** will open a new facility in Chennai for producing laptops for four leading notebook brands in India and is negotiating with several multinational electronics component companies to form joint ventures aimed at strengthening its position in component manufacturing.

**Foxconn** plans to invest CNY1 billion (\$138 million) to construct a new business headquarters in Zhengzhou, China.

**Havells India** will invest INR800 crore (\$95 million) for a new electronics manufacturing facility in the first phase of development for the first electronics manufacturing cluster in India's Uttar Pradesh state.

Hirose Electric added Master Electronics as an authorized dealer in the Americas.

India is hoping massive subsidies can help it establish a self-reliant semiconductor ecosystem.

**Jabil** will lay off 130 employees in Albuquerque later this year due to a "shift in customer demand" and completed the construction of a new production facility in Osijek, Croatia.

**Jaltek** is collaborating with **PP Control & Automation** to target new orders with UK organizations involved in indoor/vertical farming, automation, precision farming and remote sensing.

**Kaynes Technologies** in August inaugurated an advanced electronics manufacturing services unit near Hyderabad, India.

Nexperia installed Essemtec's Fox MFC pick-and-place system at its Stockport, UK, facility.

Nikon opened a 90,000 sq. ft. advanced manufacturing technology center in Long Beach, CA.

**Nordson Electronics Solutions** consolidated its European offices into one location in Valkenswaard, Netherlands.

Padget Electronics will start making Google Pixel smartphones in September.

**Pico MES** announced that all manufacturers will be able to use its digital work instruction suite of tools for free.

**Plexus** broke ground on its sixth manufacturing facility in Penang and said it is investing more than MYR1 billion (\$215 million) in Malaysia over the next three years.

Poly Electronics is adding three AI-powered inspection machines to its manufacturing lines.

**Rocka Solutions** opened a new entity in Canada to better serve its customers and expedite the delivery of import products across the nation.

**Semi-Kinetics** installed three **Koh Young** Zenith 2 3-D AOI systems and an **Epilog** Fusion Pro laser machine at its California facility.

**SK Hynix** will receive up to \$450 million in direct funding and a loan of up to \$500 million from the Commerce Department to support high-bandwidth-memory production and advanced packaging R&D in the US.

**Tata Electronics** started the construction of its INR27,000 crore (\$3.2 billion) chip assembly plant in India that will produce more than 48 million chips per day.

**TPV Technology** will implement **Blue Yonder's** supply planning solution to increase supply chain efficiency, visibility and responsiveness.

**TSMC** has taken targeted measures to boost its support for Taiwan's domestic supply chain, reduce costs, and reduce the risks associated with foreign monopolies.

**Turkey** announced \$30 billion in incentive packages to boost high-tech investment in the country, including \$5 billion to build a semiconductor factory.

**VS Industry** secured new orders in the Philippines with an aggregate value of MYR1.5 billion (\$338.5 million) over the next two financial years.

**Zetwerk Manufacturing Businesses** has announced a strategic partnership with **SMILE Electronics** to establish three new factories dedicated to IT hardware production in India.

See us at PCB West Booth #309

# pro-bond & thermal-bond

Flexible bondply materials for high-performance, high-reliability multilayer PCB stack-ups

#### Get in touch

EMEA / Peter Coakley +44 7976 946 138 peter.coakley@ventec-europe.com

Germany / DACH / Robert Art +49 173 421 4625 robert.art@ventec-europe.com

Americas / Pesh Patel +1 714 683 7825 pesh.patel@ventec-usa.com

Asia / Shawn Peh +65 96 279 906 shawn@ venteclaminates.com

venteclaminates.com

## PEOPLE

# PCDF

John Geerdes

Ram Mayampurath

Daniel Gamota

Rafael Padilla

All Flex Solutions appointed **Jamil Abdallah** manufacturing plant manager and promoted **John Geerdes** to senior process engineer.

MKS Instruments appointed Ram Mayampurath CFO.

NextFlex appointed **Daniel Gamota** executive director.

Shengyi Technology named Rafael Padilla VP of OEM marketing (North America).

Greg Beck

Michael Bowden

Victor Madero

**Bill Wentworth**

**Christopher Nash**

**Richard Burke**

GayeLyn Bates

Bob Pearson

Rosie Medina

Matt Hansen

Absolute EMS named **Greg Beck** director of sales.

Altus Group appointed Michael Bowden service and applications engineer.

Count On Tools appointed Victor Madero of SMTVYS Technology partner and distributor for Mexico.

Data I/O named **Bill Wentworth** president and CEO.

Indium promoted Christopher Nash to senior sales and business development manager.

Kyzen named **Richard Burke** key account manager.

Libra Industries appointed GayeLyn Bates senior vice president of business development.

PDR Americas appointed **Bob Pearson** representative for the Central Texas region.

Promex Industries named Rosie Medina senior vice president of sales and marketing.

QP Technologies promoted **Matt Hansen** to VP of sales and marketing.

Spectrum Advanced Manufacturing Technologies announced the retirement of CEO **Jeff Riggs** and the appointment of **Jeff Gilbert** to the position.

Unigen named John Burke president and COO.

Transform your innovation into reality™

AdvancedPCB offers comprehensive support as an extension of your product development team. We provide solutions for complex layout services, and transition your design into successful fabrication and assembly. Our designers have industry-proven experience with:

- High-speed digital

- RF and Rigid-Flex

- High-Density Interconnect (HDI)

- Signal/Power Integrity

WEST 2024

onference & Exhibition

### Visit us at PCB West!

- AdvancedPCB Booth 319

- AdvancedPCB Design Services Booth 113

## Learn More

# PCB West Exhibition Floor Sold Out

PEACHTREE CITY, GA – The exhibition floor space is sold out for PCB West, the largest exhibition and conference for printed circuit board design, fabrication and assembly in the Silicon Valley. It is the tenth time in 11 years all booths have been sold for the popular exhibition, PCEA said.

"Coming off an outstanding PCB West 2023, booth sales for our 2024 event have been strong," said Frances Stewart, vice president of sales and marketing at PCEA. "We're looking forward to another great event."

PCB West will be held Oct. 8–11 at the Santa Clara (CA) Convention Center. The event includes a one-day exhibition on Oct. 9.

This year's show will feature more than 100 exhibitors showcasing the leading companies in the PCB industry, including the top CAD and CAM vendors and top names in printed circuit fabrication and electronics assembly. Attendees will be treated to a free lunch on the show floor during the exhibition on Oct. 9.

# 'Early Bird' Discount for PCB West Technical Conference Ends Sept. 7

PEACHTREE CITY, GA – The discounted price for the PCB West 2024 technical conference ends Sept. 7. From Sept. 8 through Oct. 8, registrants will pay the advanced conference price, which is \$100 more than the "early bird" rate.

The technical program for PCB West 2024 features more than 115 hours of in-depth electronics engineering training from leading experts such as Rick Hartley, Lee Ritchey, Tomas Chester, Dan Beeker, Gerry Partida and Susy Webb.

The scope of classes ranges from designing all types of printed circuit boards to complex signal and power integrity and power delivery systems design. Foundational topics such as circuit grounding and PCB stackups are interspersed with advanced tutorials on DDR5, thermal management, analog measurements, system mechanical design, and more.

"This year's lineup of presenters is second to none," said Mike Buetow, president, PCEA. "It is literally the only place where you can meet Rick Hartley, Lee Ritchey, Susy Webb and Dan Beeker in one place. That's what makes PCB West the industry's leading event for technical information and professional networking."

Registration for the technical conference and the exhibition is open at pcbwest.com.

An exhibition featuring more than 100 leading suppliers to the electronics design, manufacturing and assembly

# PCEA Board Welcomes 2 New Members

PEACHTREE CITY, GA – PCEA in June welcomed two new board members, filling two vacated seats. The new directors both have long electronics industry experience across the design to assembly spectrum, as well as significant financial expertise.

Jim Barnes is corporate senior vice president, strategic global sourcing at Generac, a leading energy technology company. Prior to that, he spent more than 15 years in management at a publicly traded multinational EMS company. He is an expert in strategic planning, team building, finance, outsourcing, manufacturing operations best practices, supply chain, and business development, with experience in the US, Mexico and Asia.

Matthew Leary has been designing PCBs full-time since 1996. He is the founder and president of Newgrange Design, a Boston-area PCB design service bureau. His design work has included high-speed, high-voltage, high-power, high pin count, low-level signals, and more. He is a graduate of the University of Wisconsin-Madison with a degree in physics.

Jim Barnes

Matt Leary

# CPCD Course to be Offered at Wayne State in 2025

PEACHTREE CITY, GA – Wayne State University will offer PCEA Training's Certified Printed Circuit Designer curriculum as part of a semester-long course on printed circuit board design starting in January.

The Detroit-based school, the third largest in Michigan, gained experience with the course last summer when it held a CPCD class of approximately 35 students in June.

Students will be taught the entirety of the CPCD course, which includes the Printed Circuit Design Professional

handbook, a 400-page guide of technical information that provides the knowledge base for making good decisions in the printed circuit engineering process. Wayne State plans to add lab work and talks from local manufacturers as part of its course, and will use the CPCD certification exam as its final exam.

# PCB East 2025 Conference Task Group Named

PEACHTREE CITY, GA – The PCEA Conference Task Group named its PCB East 2025 members.

Troy Hopkins, a printed circuit design professional and consultant, leads the group as chairman alongside eight other printed circuit industry veterans.

Other industry experts in the task group include John Burkhert Jr., Stephen Chavez, Tomas Chester, James Jackson, Keith Kowal, Matt Leary, Matt McBride, and Susy Webb.

"Building off the continued growth of last year's conference, I am thrilled to bring together this exceptional group of industry experts," said Hopkins. "Their experience and collective wisdom will help ensure PCB East 2025 will showcase content that addresses the challenges facing PCB designers as well as showcasing the latest innovations and best practices in PCB design and manufacturing.

"With this group I am confident this conference will continue to provide massive value, empower PCB designers, and bring our industry together."

PCB East is the largest technical conference and exhibition for the electronics design, fabrication and assembly industry in New England.

The four-day technical conference takes place Apr. 29 – May 2 at the Boxboro Regency in Boxborough, MA, with a one-day exhibition on Apr. 30. For details, visit pcbeast.com.

## PCEA CURRENT EVENTS CH

### **CHAPTER NEWS**

**General.** The annual PCEA meeting will be held Oct. 8 from 9 – 10 a.m. during PCB West at the Santa Clara (CA) Convention Center. An update on all association programs, plus the annual awards, will be presented.

Abstracts for next year's PCB East technical conference are due Sept. 6. The conference, the largest of its kind in New England, will take place Apr. 29 – May 2, 2025, in Boxborough, MA. The event includes a one-day exhibition on April 30. Submit abstracts here.

Some 78% of respondents to PCD&F's annual Salary Survey said they would find value in an online

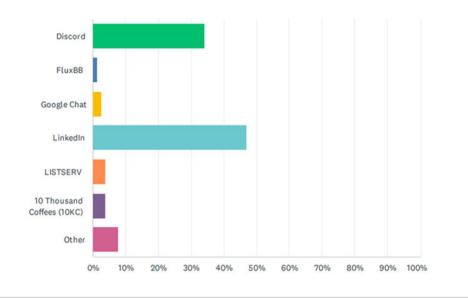

networking forum dedicated to printed circuit board design and engineering. When it comes to the type of forum, however, the responses were varied. LinkedIn was the top choice, at 47% of respondents. Discord was second, at 34%. No other option received more than 5% of the votes cast.

LinkedIn and Discord are the preferred forums for designers/design engineers to network online.

**Portland, OR.** In August we welcomed Bill Loving of ScanCAD International for a discussion about PCB reverse engineering. We will hold a live meeting at Axiom Electronics in October. Those interested should email sschmidt@pcea.net.

**San Diego.** Our meeting on Aug. 20 featured Mark Finstad, director of engineering at Flexible Circuits Technologies. Chapter members enjoyed a presentation on flex circuit design and manufacturing over lunch.

Mark Finstad talks at the San Diego chapter meeting in August.

# foremost in FORMULATION

We offer custom adhesive and encapsulation solutions

**LEARN MORE**

# Electronics Industry Sentiment Rose at end of July

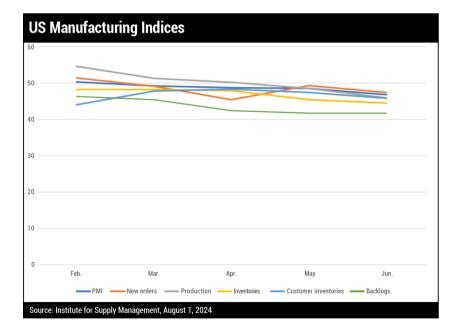

BANNOCKBURN, IL – Sentiment in the electronics industry saw a modest uptick in August, though it remains below the peak observed in April, IPC said in a report released in mid-August. The results are based on a survey conducted Jul. 18-31.

Regarding current supply chain conditions, half (50%) of electronics manufacturers responding said they are currently experiencing rising labor costs, with 46% reporting increased material costs. At the same time, ease of recruitment, profit margins and backlogs are presently declining. Over the next six months, electronics manufacturers expect labor and material costs to remain high, although relatively stable. Profit margins and backlogs are expected to rise, with recruitment challenges continuing to persist.

Some 42% of respondents are very or extremely concerned about geopolitical risks and 44% are concerned with trade policies and tariffs, with no significant differences by geographical regions.

Additional survey data show:

- The demand index increased 3.3% in August, fueled by better, albeit still contracting, backlog, capacity utilization that shifted to expansion, and heightened order sentiment.

- Cost pressures eased slightly in August, with indices for labor costs and material costs each dropping one point. Despite the declines, both indices remain in expansion territory, indicating a majority of businesses continue to face cost challenges. Notably, the labor costs index hit a new low for the year.

- The overall industry outlook remained robust in August, although demand sentiment has cooled from earlier highs this year.

|                                            | % CHANGE |                  |                   |      |  |

|--------------------------------------------|----------|------------------|-------------------|------|--|

|                                            | APR.     | MAY <sup>r</sup> | JUN. <sup>₽</sup> | YTD  |  |

| Computers and electronics products         | 0.0      | -0.4             | -0.3              | 1.2  |  |

| Computers                                  | 3.8      | -1.1             | -2.3              | 23.7 |  |

| Storage devices                            | 1.7      | 0.0              | -6.4              | 6.5  |  |

| Other peripheral equipment                 | 5.4      | 0.5              | 0.2               | 4.5  |  |

| Nondefense communications equipment        | 0.0      | -2.2             | 2.2               | -0.2 |  |

| Defense communications equipment           | 1.5      | -2.0             | -2.0              | -2.1 |  |

| A/V equipment                              | -7.1     | -3.9             | -1.3              | 15.3 |  |

| Components <sup>1</sup>                    | 1.0      | 0.9              | -1.3              | 6.3  |  |

| Nondefense search and navigation equipment | 2.2      | -0.9             | 0.2               | 1.9  |  |

| Defense search and navigation equipment    | 0.4      | 0.4              | -0.9              | 5.8  |  |

| Electromedical, measurement and control    | -0.3     | -1.0             | 0.1               | -1.2 |  |

Source: US Department of Commerce Census Bureau, August 2, 2024

| Key Components                                                                      |                   |        |        |       |        |  |  |

|-------------------------------------------------------------------------------------|-------------------|--------|--------|-------|--------|--|--|

|                                                                                     | FEB.              | MAR.   | APR.   | MAY   | JUN.   |  |  |

| EMS book-to-bill <sup>1,3</sup>                                                     | 1.31              | 1.42   | 1.36   | 1.32  | 1.21   |  |  |

| Semiconductors <sup>2,3</sup>                                                       | 15.2%             | 15.8%  | 19.3%  | 18.3% |        |  |  |

| PCB book-to-bill <sup>1,3</sup>                                                     | 1.13              | 1.06   | 0.96   | 0.95  | 0.99   |  |  |

| Component sales sentiment <sup>4</sup>                                              | 106.9%            | 124.1% | 112.3% | 98.9% | 103.4% |  |  |

| Sources: <sup>1</sup> IPC (N. America). <sup>2</sup> SIA. <sup>3</sup> 3-month movi | ng average. ⁴ECIA |        |        |       |        |  |  |

# Hot Takes

Sales of **PCB materials** (excluding flex) dropped 16% year-over-year to \$57 billion in 2023. Copper-clad laminate sales made up about \$13 billion, including prepreg but excluding mass laminate. Some 650 million sq. m. of rigid

laminate materials, including paper, composite, FR-4, and specialty laminates were sold, down slightly from 2022. (Prismark)

The global **flex PCB market** will gradually recover from its 2023 downturn, with the market size expected to reach \$19.7 billion in 2024, representing a 7.3% year-on-year growth. (TPCA).

Japan's PCB output has shrunk for 19 consecutive months through May, but the decline has only been in the single digits for the past three months. (JPCA)

North American PCB shipments in July fell 21.2% versus a year ago and sank 14% sequentially. Bookings were down 25.4% and 17.3%, respectively. (IPC)

The **European PCB industry** saw a year-over-year decline in billings of 6.5% during the first half of 2024. (Data4PCB)

North American EMS shipments in July rose 1.9% over July 2023 and were up 1.9% over June. Year-over-year bookings increased 0.2% and quarter-over-quarter bookings rose 0.1%.

Packages using chiplet architectures will grow at 69% compounded annually from 2023 to 2029. (TechSearch International)

Worldwide silicon wafer shipments in the second quarter declined 8.9% year-over-year, but rose 7.1% quarterover-quarter. (SEMI)

Major PCB and IC substrate manufacturers from Taiwan are expanding operations in Southeast Asia but face sustainability challenges amid uncertainties of electricity and water supply. (DigiTimes)

Three EMS transactions were recorded in the second quarter, down from five recorded in 2023's second quarter. (Lincoln International)

Global **semiconductor sales** totaled \$149.9 billion during the second quarter, an increase of 18.3% compared to 2023 and 6.5% more than the first quarter of 2024. (SIA)

Taiwan's export orders rose more than expected in July as **demand for chips used in artificial intelligence applications** continued to soar and the government said it expects the momentum to extend into August. (Taiwan Ministry of Economic Affairs)

Taiwan-based ODMs are cautiously optimistic about **consumer electronics product demand** in the second half of this year, according to industry sources. (DigiTimes)

DRAM sales saw revenue growth of \$22.9 billion in the second quarter, a sequential rise of 24.8%, on higher shipments of mainstream products. (TrendForce)

The amount of **data center supply** under construction in North America's top markets jumped by about 70% compared to a year ago to a record 3.9GW. (CBRE Group)

Worldwide spending on **artificial intelligence**, including AI-enabled applications, infrastructure and related IT and business services, will more than double by 2028 to \$632 billion. (IDC)

North American **EMS shipments** in July were up 1.9% compared to 2023 and increased 1.9% sequentially. Bookings increased 0.2% year-over-year and 0.1% from the previous month. (IPC) **=**

# FUJI AMERICA'S ANSWER TO SMART STORAGE SOLUTIONS

NEW/ LOGISTIC SOLUTIONS

SMD BOX MIMO G3

Neotel's innovative take on the SMD Tower, offers batch processing for SMD reel materials, supporting loading via trolley or AGV.

# POWERED BY SMART MATERIAL FLOW

More SMD Box Series!

- >> SMD BOX SISO

- SMD BOX MIMO

- SMD BOX DUO

- SMD BOXi

- SMD BOX ONE

- SMD BOX XLC

- SMD BOX SP

- SMD BOX HYBRID

WE CAN HELP YOU SOLVE

HOW TO

() MA

MATERIALS

CONTACT US NOW TO SEE OUR FULL LIST OF SMD BOX SOLUTIONS AND MORE!

fujiamerica.com

Distributed by

America Corporation

© Fuji America Corporation. All rights reserved. 171 Corporate Woods Pkwy, Vernon Hills, IL 60061 847.913.0162 info@fujiamerica.com

### From Microns to Nano

#### PCB designs will soon enter a new dimension in miniaturization.

OUR INDUSTRY HAS always been about creating cutting-edge, next-generation technology. Over decades this has been accomplished by striving to pack more capability in less space. The electronics industry, and printed circuits in particular, has accomplished this more often than not without specific definitions to either strive for, or be hindered by.

Such examples can be found by looking at the definitions, per Oxford Languages, for five simple words that have been used over the decades in our technologically driven businesses:

- Normal defined as "usual, typical or expected"

- Small defined as "of a size that is less than normal"

- Compact defined as "closely and neatly packaged together; dense"

- Miniature defined as "if a much smaller size than normal"

- Dense "closely compacted in substance."

Clearly, the definition of each word has, shall we say, an open interpretation as it relates to technology, dimensions and tolerances! And yet, over the decades, engineers speaking and working on next-generation projects have had more than a good idea of what, at that point in time, each word meant.

In the early 1990s, if you were fabricating printed circuit boards, "normal" was defined as a board with 7-mil lines and spaces. "Small" referred to something along the lines of 5-mil lines and spaces. "Compact" would have included a panel of circuit boards that were V-scored to get as many as possible on the panel. "Miniature" was a dream: lines and spaces of less than 5 mils. And "dense" referred to how thin the combined layers on a multilayer circuit board can be.

That was then, now is now. New words are entering the vocabulary of designers and fabricators. The days of using terms with open-ended interpretations when defining the goal of getting more capability into less space has finally given way to the use of words with more specific dimensional definitions.

"Micron" has been used for years in the discussion of dimensions and tolerances sought when designing and fabricating circuit boards. Micron is a metric unit of length equal to one *millionth* of a meter. Developing the processes and materials to support micron technologies' ultra-minute dimensions is a formidable task that is still underway, but it has yielded highly successful results.

Today, micron plating thicknesses and the ability to plate in microns is common. IPC standards define acceptable plating thicknesses in microns. Suppliers of PCB materials use microns in their specifications. Imagining the ability to plate or image in microns was once a dream. Today, while still cutting-edge, holding dimensions and tolerances in microns is commonplace, and micron technologies are standard in the greater electronics industry.

Another word gaining traction in our industry is "nano." "Nano" is a short for "nanotechnology," which is a metric unit of length equal to one *billionth* of a meter. If producing printed circuit boards with dimensions in microns is cutting-edge, producing circuit boards with nano dimensions is nothing less than bleeding edge! But as intimidating as the thought of nano dimensions may be, developing processes and materials is how our industry, over and over, has been able to develop bleeding-edge technologies that eventually become industry standard.

If micron is today considered "normal," then new processes and materials necessary to establish nanotechnology within the printed circuit board industry will undoubtedly go through various iterations and phases of research, development and refinement. These combined efforts will be more interesting, as well as more challenging, than those of the past, in large part because the size – the actual dimensions – have far exceeded the ability for the unaided human eye to observe.

Equally, some of the products in which nanotechnologies will be utilized may also be too small for the human eye to see unaided. As dimensions shrink, so can the packages they go into.

So here we are again, as we have been countless times over the decades; an industry working on the next challenge. This time it is taking the current "normal" of micron technology, and by diligently working to transition processes and materials, moving from "small" to "compact," "miniature" to "dense," until we achieve the next baseline for "normal," which will shortly be nanotechnologies. Onto the next great challenge, and repeat. **«P**

**PETER BIGELOW** is president of FTG Circuits Haverhill; (imipcb.com); pbigelow@imipcb.com. His column appears monthly.

# ENSURE OUALITY & COMPLIANCE FOR RINSE WATER TREATMENT & REUSE

Wastewater ion exchange (WWIX) is a service-based solution ideal for the treatment of circuit board production and assembly rinse waters. Coupling this technology with predictive analytics takes water treatment and recovery to the next level.

#### How Can WWIX Help Your Facility?

Smart water recovery solutions maximize water quality & process uptime while minimizing facility involvement.

Small system footprint and up-front investment while driving both water sustainability and compliant recovery of waste metals.

Network of 110 local services branches across North America to provide the fastest response times in the industry.

Contact us to learn more +1-800-466-7873

## Let's Stop Idolizing Ourselves

#### Self-confidence comes from meeting new challenges.

I SHAKE MY head when I see the large amount of self-idolizing today on LinkedIn. Who describes themselves as visionary, disruptive, a rainmaker, the prophet, the catalyst, the wizard, a guru, a Jedi master, or a creative genius?

Do you feel that this hubris is believable to peers? When did our egos start to dilute the need for getting up every day, working hard, looking at problems from multiple angles, being bold to take mindful chances, understanding we make our own luck and being thankful for small victories when running a business? Your title is stated on your business card; use it.

Disruptive people, technologies or real advancements in our society are so few, it seems we now must minimize these people or events when they actually occur due to the overuse of this term. For most of us, success is a byproduct of very hard work, learning from failures, collaboration with the people we are surrounded by, an ability to see the real issues affecting our businesses with a focus on solving the critical few, a strong competitive drive for "winning," and yes, a little good luck.

Winning deals or awards is both an exhilarating and a humbling experience, but not something to dwell long on as the next challenge is always right around the corner. Outstanding business results simply gave us the right to wake up and fight a new fight the next day; it's our job and people are counting on us to perform. Those people counting on us are our families, customers, shareholders, stakeholders and vendor base.

I feel that a degree of "working scared" has driven excellent results for the successful EMS professionals I know. Selling scared wasn't a fear of being successful or entering a challenging opportunity; it was the fear of "losing" and not doing your best to outplan and outperform the competition. It's a fear to deliver less than the desired outcome you have been tasked to do. It was a fear of not meeting a deadline that people were counting on or the fear of taking too long to respond to someone who reached out to you earlier in your busy day.

The defining competitive spirit to enter a contested deal, maybe with the weaker team solution but driven to outsell the competition, has resulted in many wins in our work history. Writing the best technical response to an RFI, taking time to really understand the needs of a prospect and offering solutions, getting to your factory before an audit to run a mini-audit yourself, preparing the factory on roles and responsibilities for every audit, managing the arduous task of getting a quote just right, producing marcom content that can be used at the right time from a sales tool kit that defines who you are and who you aren't ... these are the moves that separate the EMS sales professional from the sales hobbyist.

The difference between self-confidence and self-idolization is big. To me, self-confidence is earned over time after numerous failures where you learn lessons that stay with you forever. At some point in our lives, we should realize we now know what we know, and work to fill gaps of what we don't.

Self-idolization, on the other hand, can be hatched overnight with a post, a self-described title or the simple claim you have arrived and the world should take notice.

With a good sense of who you are and over time, the wins are a little less celebratory and the losses don't drive you into a depression. You simply look forward to the next opportunity to compete and try to outperform your competition.

Once you have achieved years of successes, the world you want to compete in will take notice and will want you on their team. Empty or exaggerated claims of superiority support no purpose other than stroking an overinflated ego. Those who start to believe a self-idolizing status tend to lose whatever edge they once had and spill into mediocrity.

Still inclined to describe yourself in these terms? Perhaps you should adopt the funniest title I've seen: "President of Awesomeness." 🜗

JAKE KULP is founder of JHK Technical Solutions, where he assists OEMs and EMS companies with optimizing demand creation offerings and deciding when and where to outsource manufacturing. He previously spent nearly 40 years in executive roles in sales and business development at MC Assembly, Suntron, FlexTek, EMS, and AMP Inc. He can be reached at jkulp@cox.net.

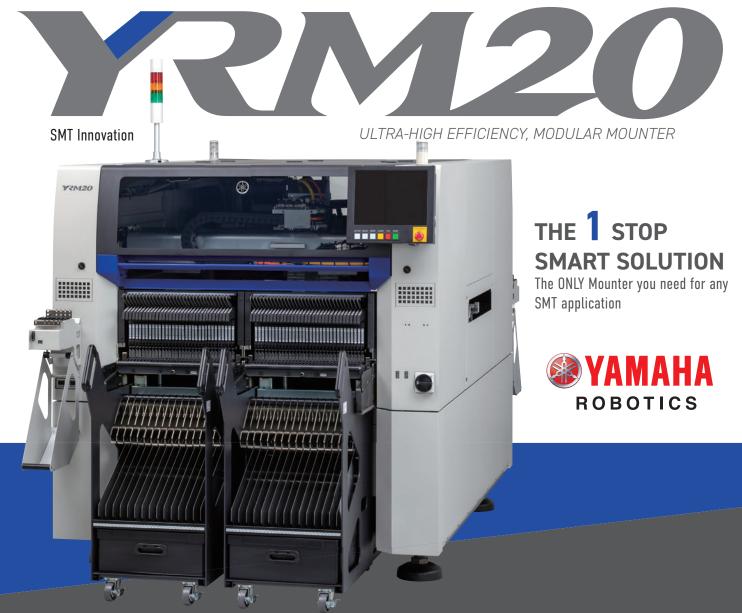

# YAMAHA'S **REVOLUTIONARY M**OUNTER

The most adaptable surface mounter, providing unparalleled productivity and operational efficiency. The YRM20 is able to handle the most challenging applications with ease.

- 115,000 components per hour

- Single or Dual Beam, optional Dual Lane

- PCB sizes: L50×W50mm to L810×W510mm

- 25µ accuracy

- Superior component range eliminates the need for head changes, even for the most complex assemblies

- Exceptional component range from 0201mm to 55x100mm, up to 30mm tall

- Up to 128 unique components on a single machine

- No-Splice, Auto-Loading Feeders

- Exchangeable, Automatic Tray Stacker

- Real Time unique 2D barcode identification and vacuum monitoring.

- Complete Automatic Changeover

- Standard Onboard Nozzle Cleaning System

Contact Yamaha Robotics Today to learn more... Visit www.yamaha-usa-robotics.com

# Is Thailand the World's Next PCB Manufacturing Base?

#### The country's growing industry could prove a viable alternative to China.

I HAVE BEEN involved in the electronics manufacturing industry for over 20 years, with much of that time based out of Hong Kong. China is a manufacturing powerhouse, supplying not only the world but its own large population with electronic products ranging from home appliances to ultra-modern electric vehicles. China is well beyond being called a "developing nation." It is a very mature economy – especially when it comes to any kind of manufacturing.

Recent geopolitical tensions from past and present US administrations, however, as well as supply chain concerns that came about during the Covid pandemic, have forced many OEMs and EMS companies to look elsewhere for their PCB needs – a task that is easier said than done.

In response to industry demands, I have traveled to several countries in southeast Asia over the past 18 months to learn as much as I can about the printed circuit board industry outside of China.

It was during my third and most recent trip to Thailand last July that I attended Thailand Electronics Circuit Asia 2024 (THECA), the electronics circuits and services showcase event in Bangkok.

The event did mark a milestone, as interest in Thailand's future in PCB manufacturing is booming. In fact, from January 2023 to June 2024, investment applications for PCBs totaled over \$3.9 billion compared to an average of \$420 million for the same period in 2021 to 2022, according to the Thailand Board of Investment.

The Board of Investment is expecting more than \$1.4 billion in investments from Chinese EV OEMs to set up manufacturing hubs to supply Asia, which has presented many opportunities for these new factories. BYD, one of the largest EV car manufacturers in the world, opened its first factory in Thailand in July.

Interestingly, most of the PCB manufacturers exhibiting at the show were from China or have factories being built in Thailand that are owned by Chinese PCB manufacturers or their investors.

Thailand has always had a strong PCB manufacturing base when it comes to low-mix and high-volume manufacturing. Like most other countries trying to mimic China's success, however, it falls short when it comes to higher-mix, lower-volume, and higher-technology PCB manufacturing. That said, since early 2022, over 20 prominent PCB manufacturing companies from China, Hong Kong and Taiwan are planning or are currently building PCB manufacturing facilities in Thailand to expand the globalizing of their manufacturing capacity. It is hoped this expansion brings opportunities. But it will also bring challenges as this is the first time some of these PCB manufacturing companies have invested heavily outside China.

During the show, I was able to talk to several general managers from different factories that are being built one to two hours outside Bangkok. These China-based managers have plenty of industry experience and were sent to Thailand to oversee the construction of their respective new facilities.

While they originally anticipated starting production earlier this year, the shortage of construction workers, the global economic slowdown and the uncertainty of incoming orders has forced these factories to most likely start operations later this year.

The output of these facilities will be gradual, with their first phase expected to produce 40,000-50,000 sq. m. per month, using upwards of 300 employees each. Several of these new factories plan to cater to customers that require high-mix, low- to high-volume and higher technology. This capability is very important as Thailand has generally catered to low-mix, mid- to higher-volume orders that are not as conducive to the US market.

These managers are facing cultural and operational obstacles, including finding enough technical operators and engineers for their factories. With over 20 large PCB facilities currently manufacturing or about to begin operations in Thailand, machine operators, engineers and chemists are in high demand.

High demand means short supply and many established domestic factories have had technicians and engineers hired away by these manufacturing newcomers. The need for experienced personnel and PCB engineering training cannot keep up with Thailand's high demand.

Language is another barrier among the Chinese and local Thai workers, as some managers say it takes upwards of a year for a factory to become a cohesive operation.

To help increase the employee supply base, several of these new facilities plan to send their Chinese employees to Thailand to train local hires, as well as source labor from outside Thailand.

Factories not only need employees but also need a supply chain to support their operations. While Thailand does manufacture raw materials, a major Chinese laminate supplier intends to open a new facility by Q4 2025.

The pricing for PCBs manufactured in Thailand is 10-15% higher than China. For now, the 25% US-imposed tariff does not apply to PCBs manufactured in Thailand. That is good news, but the average time to ship orders is much longer, averaging six to eight weeks. In comparison, China ships most product in three to four weeks or less.

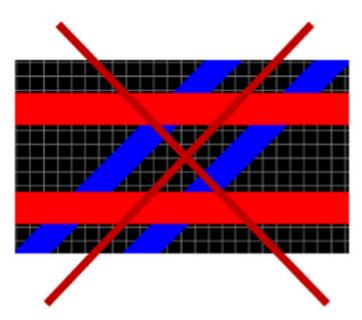

The next 18-24 months will determine how successful Thailand will become as a PCB manufacturing powerhouse. The strength of the world economy and the politics that are put into play will determine the outcome.